€1,490.00*

In Stock, delivery time: 1-3 days

Product number:

HL02302

Product information "iBasso D16 Taipan"

iBasso D16 TAIPAN

- Unrivalled performance & The best portable 1-bit discrete DAC from iBasso

- FPGA Master2.0

- 16 sets of cascaded 8E PWM DACs

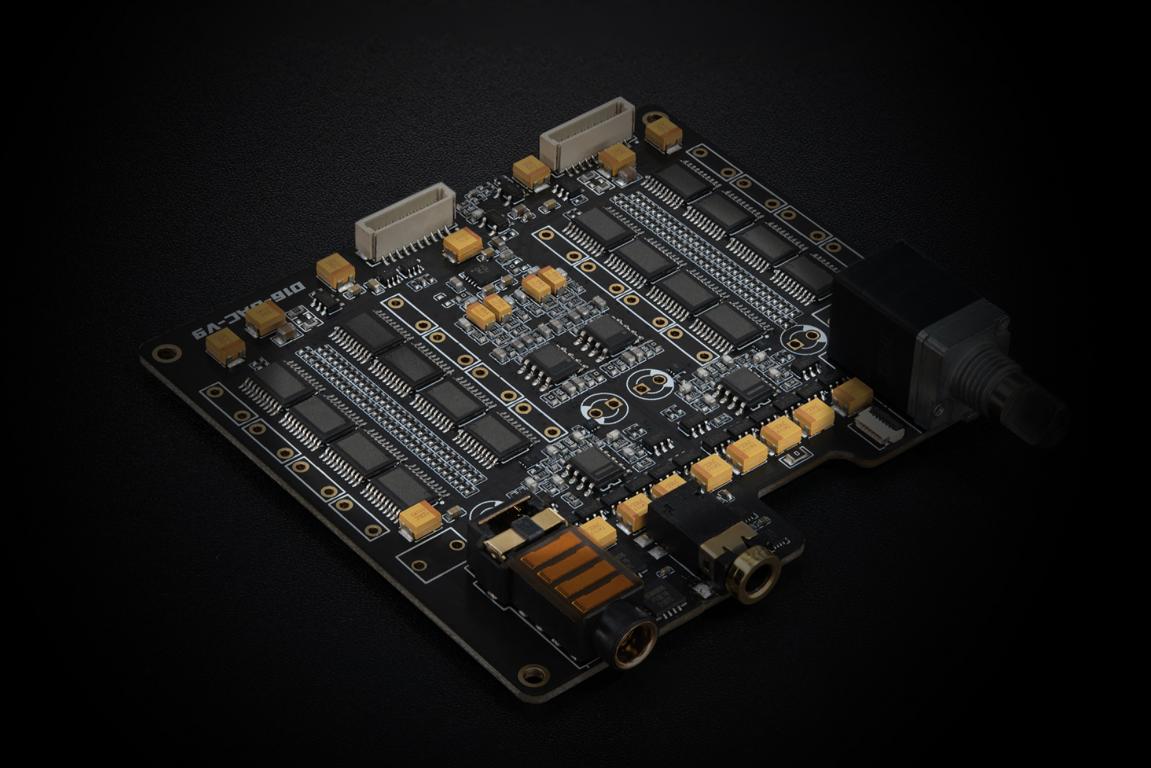

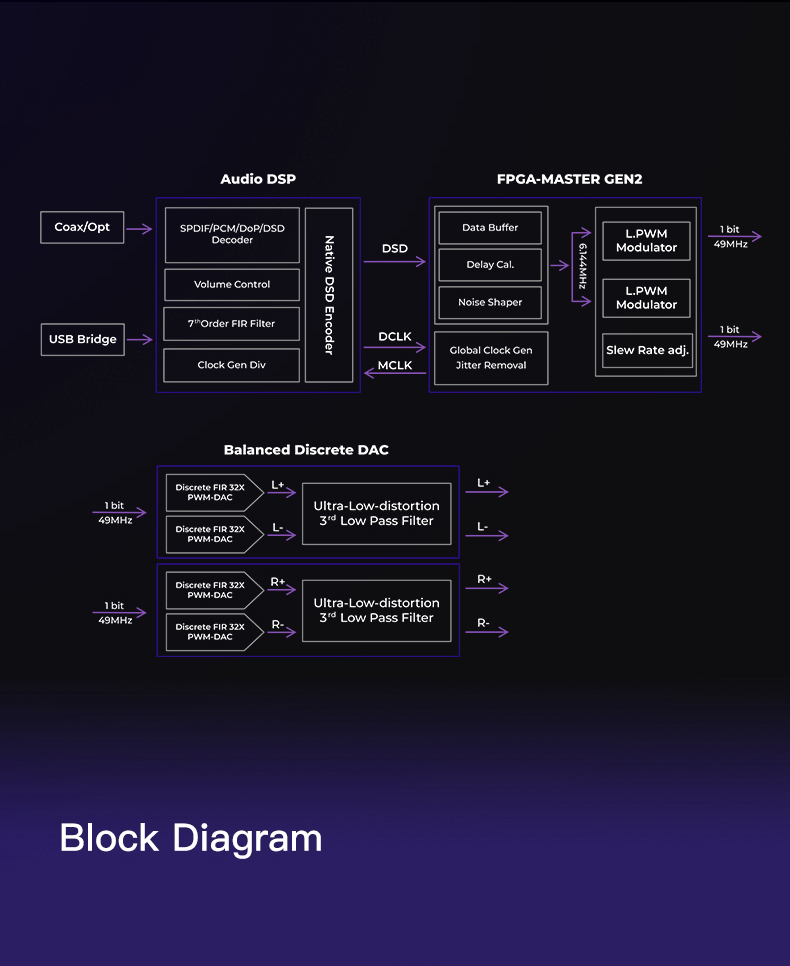

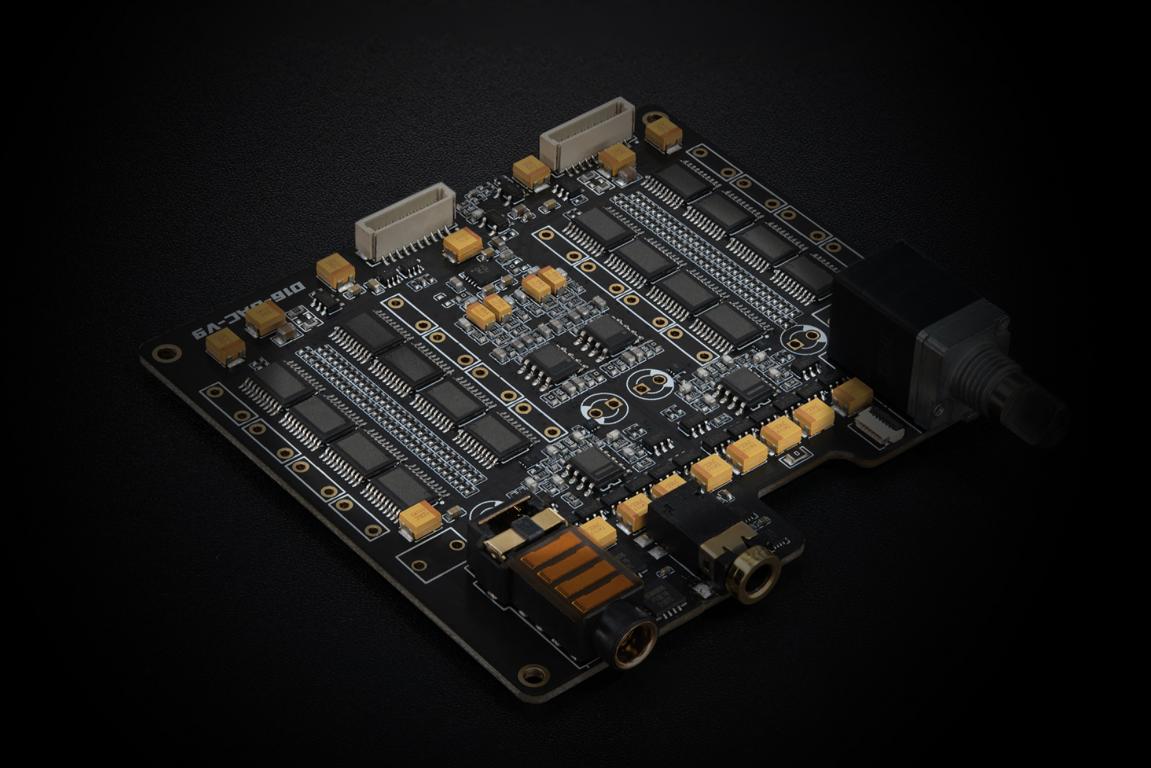

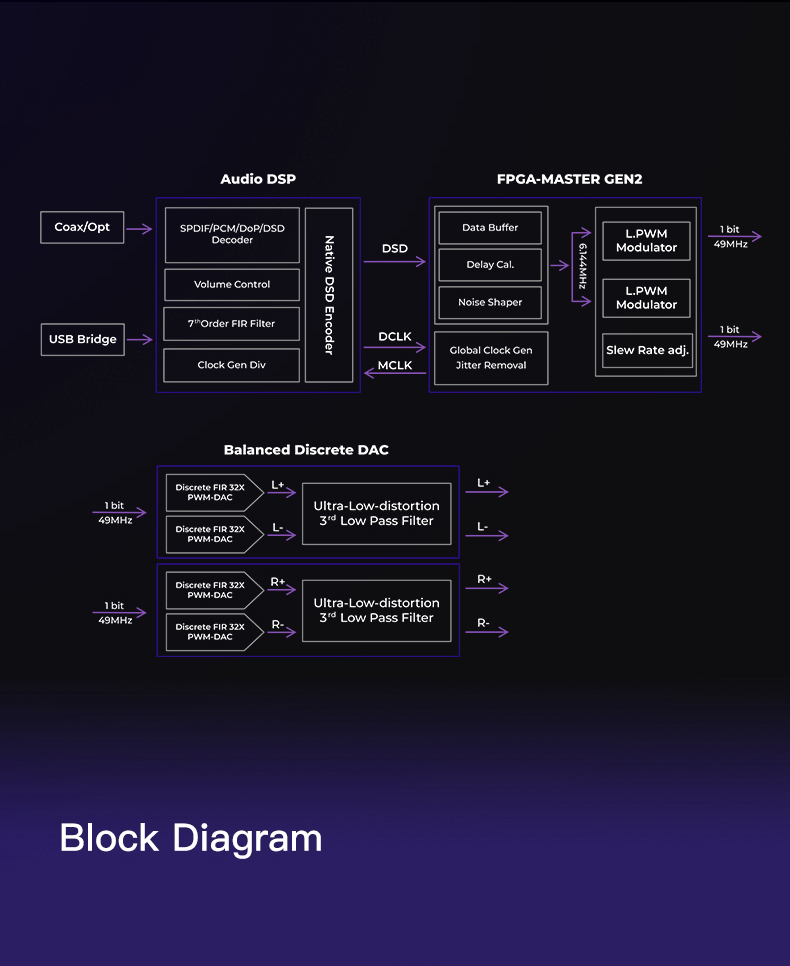

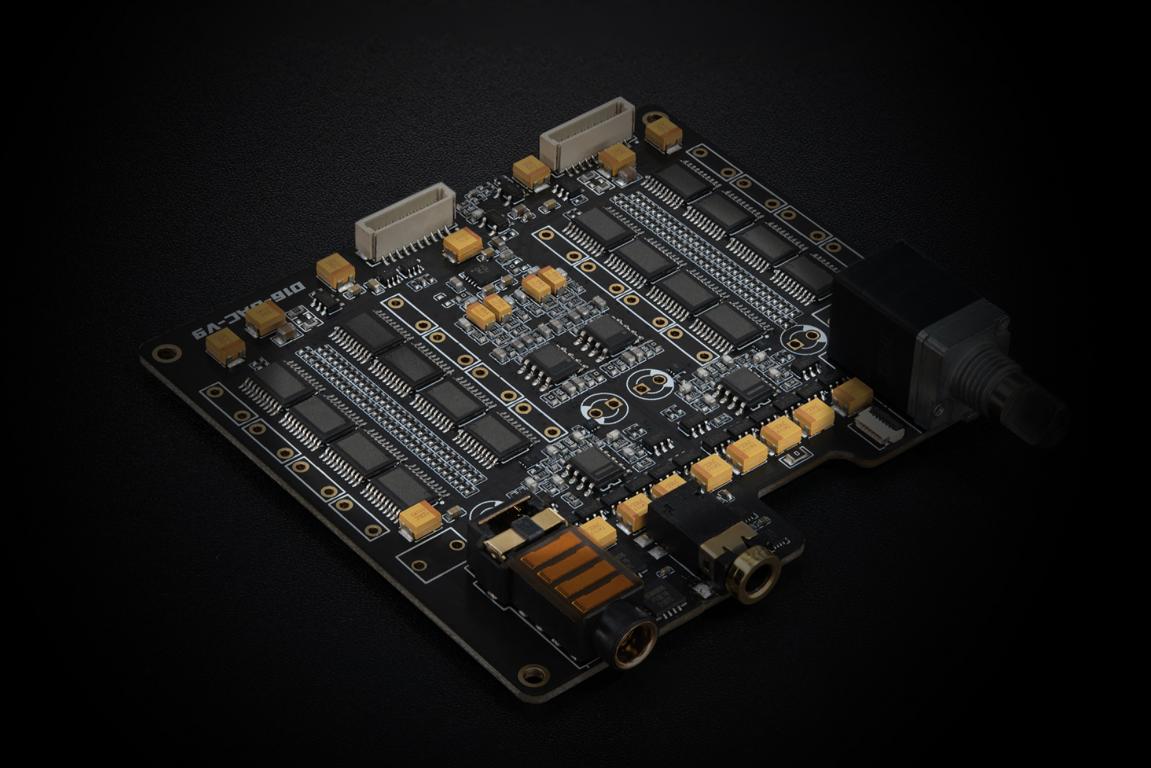

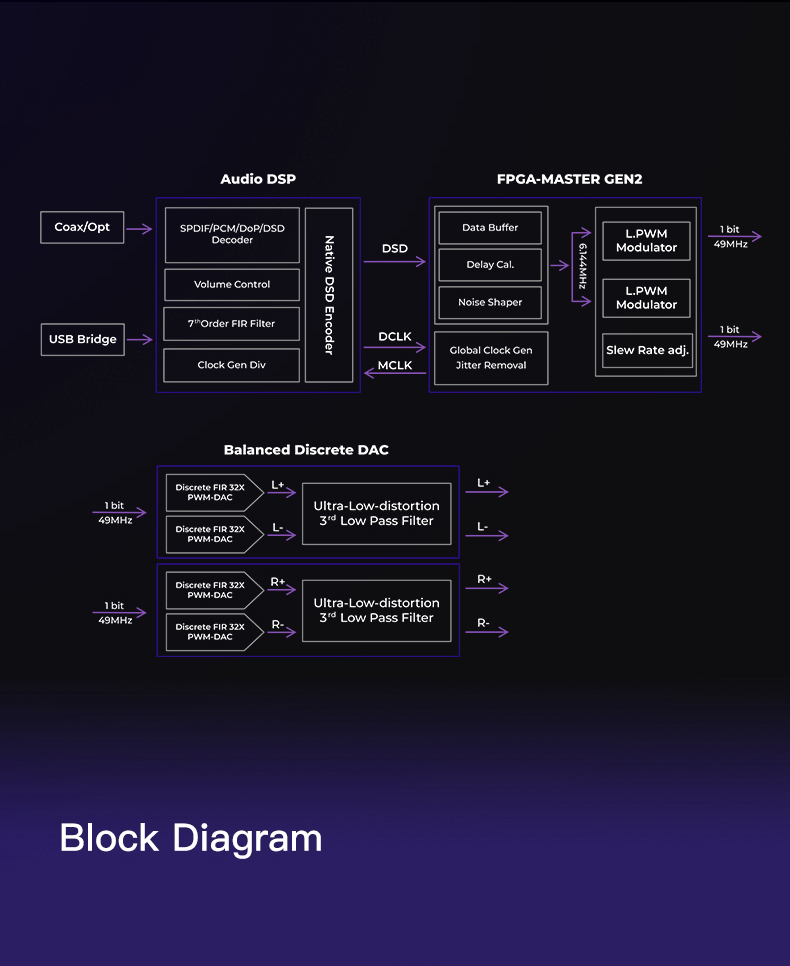

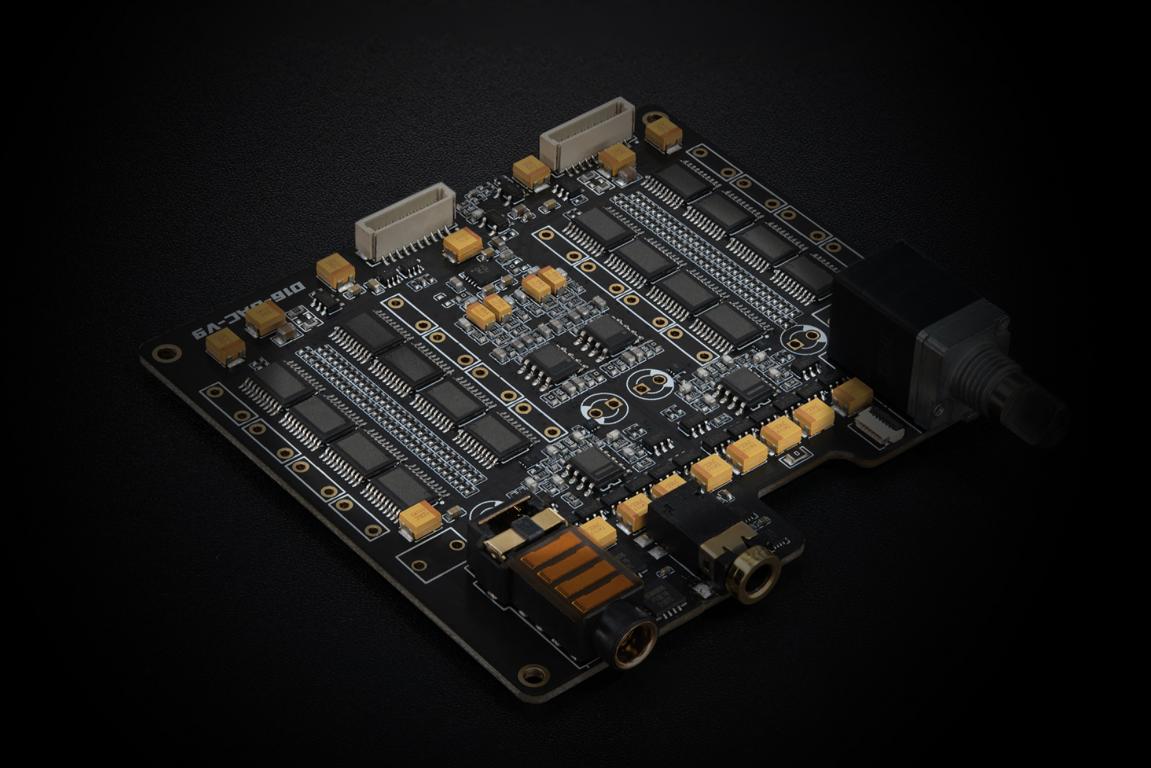

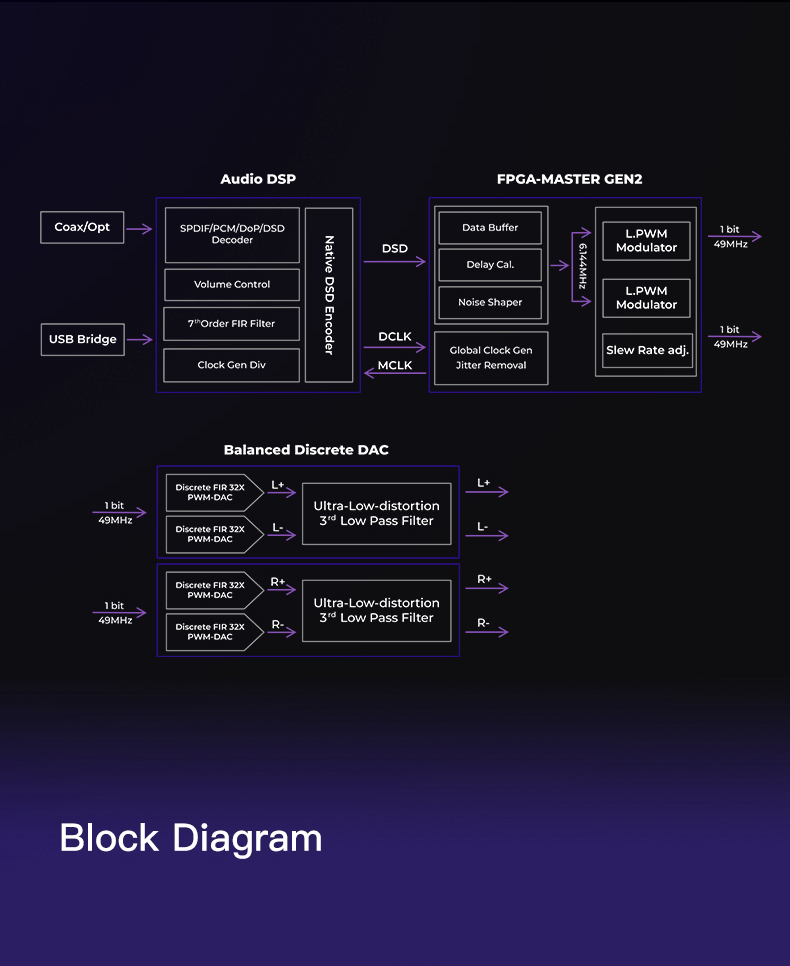

The iBasso D16 is a DAC that uses the iBasso-developed FPGA-Master2.0 as its core and utilises 16 sets of cascaded 8E PWM DACs with a total of 128 PWM DACs (discrete) for 1-bit D/A conversion. The measured THD+N value is over 0.0001%, which is the best value among current portable discrete DACs. The AMP section is a super class A transistor amplifier very similar to the iBasso DX320 MAX amplifier.

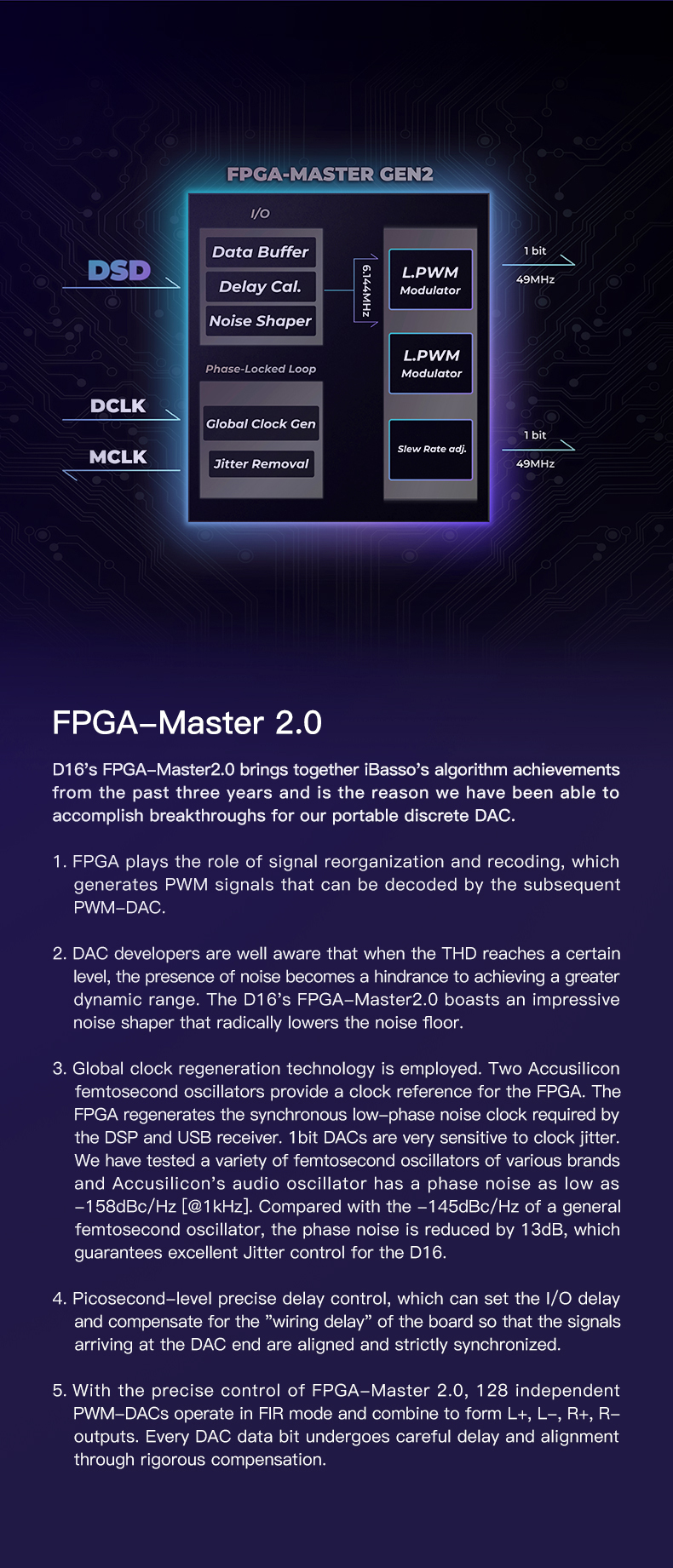

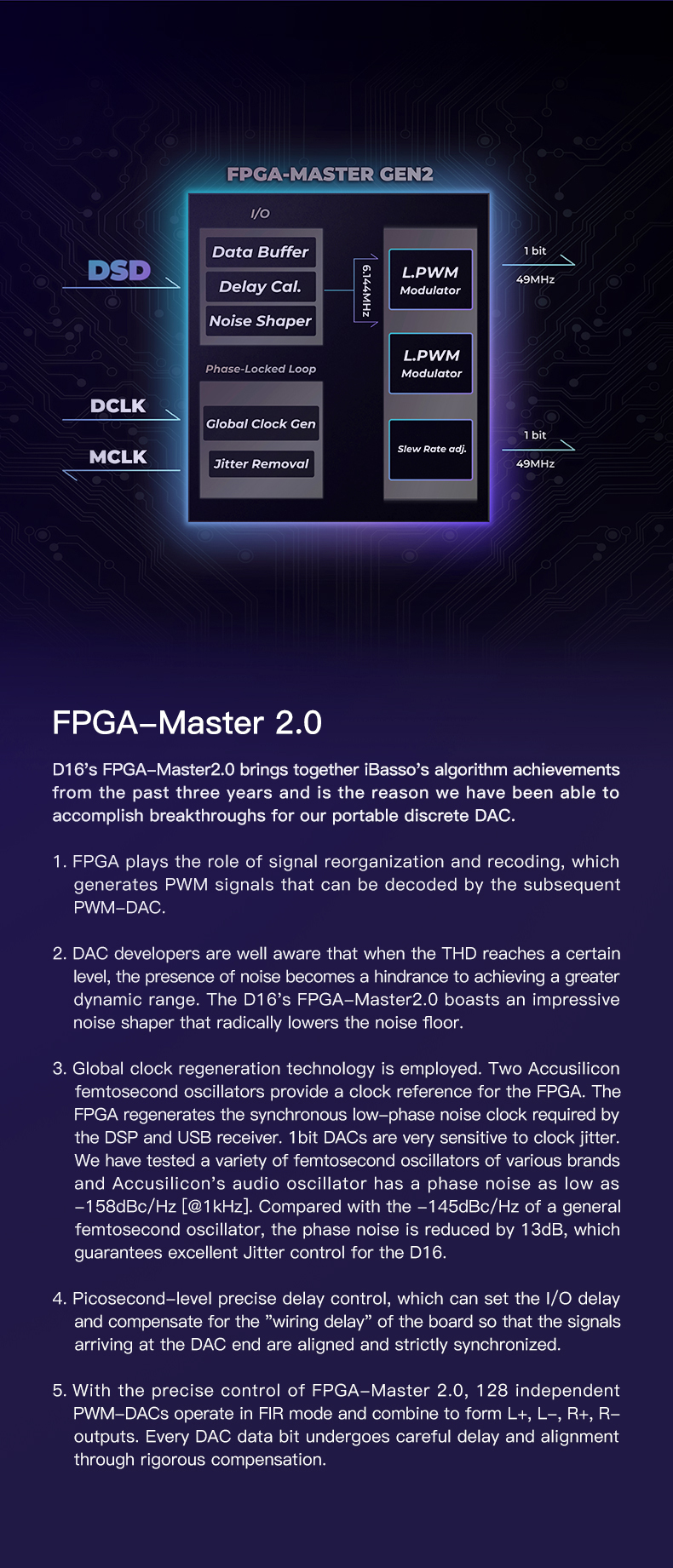

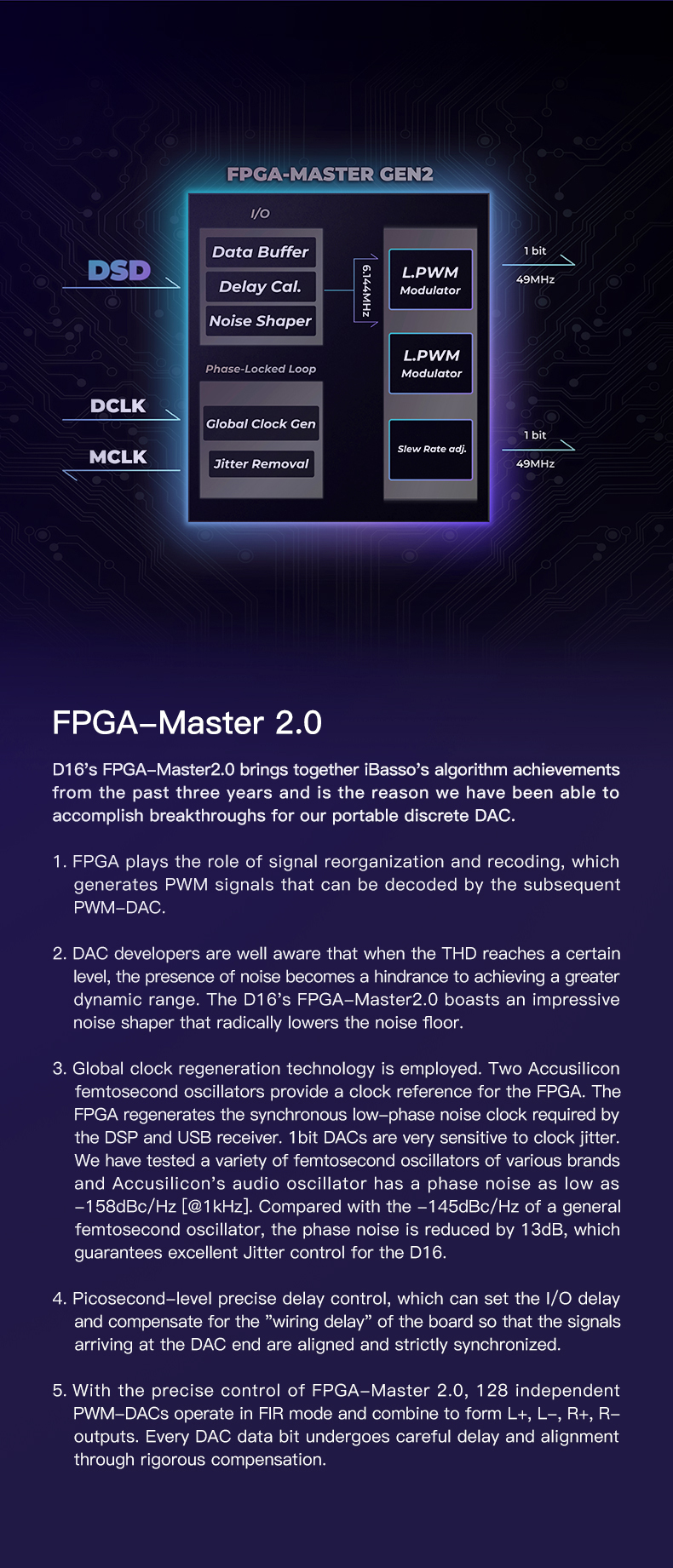

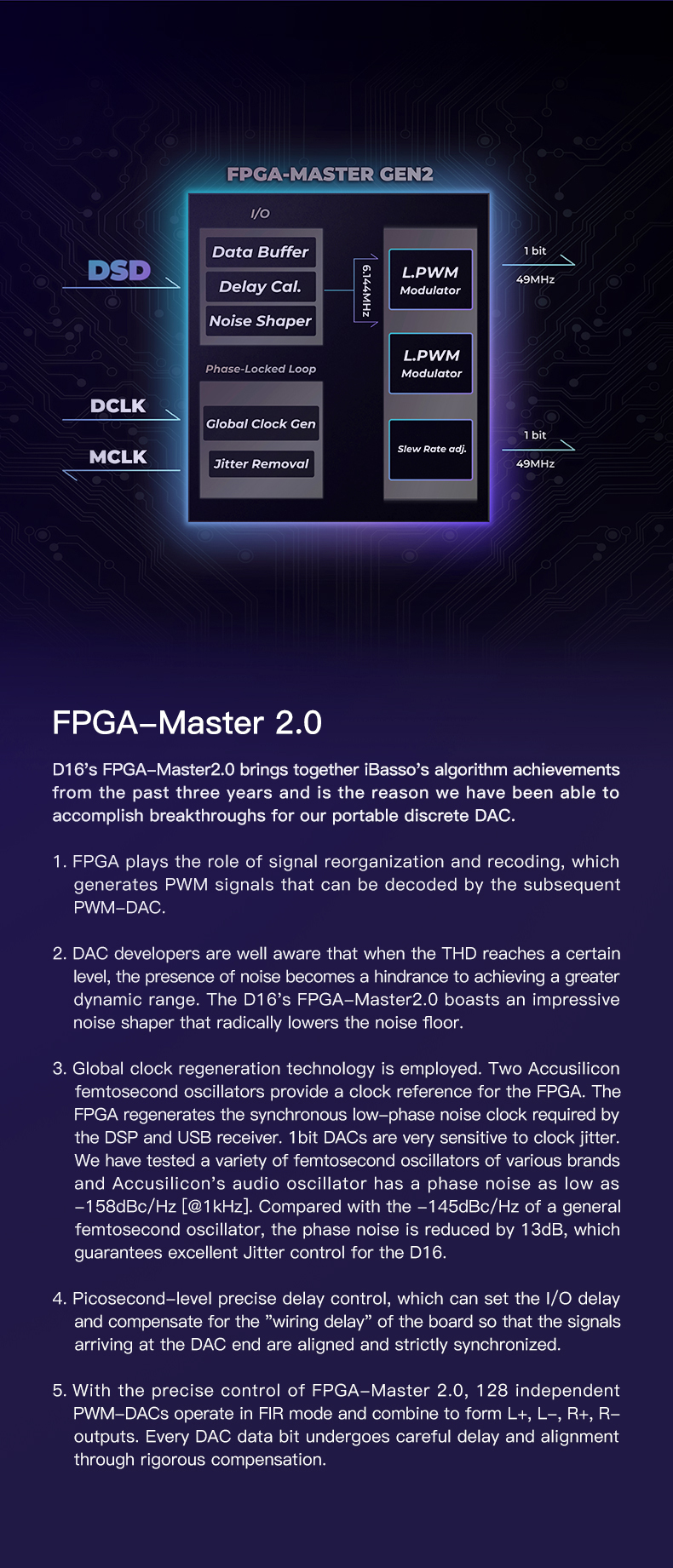

FPGA Master 2.0

The D16's FPGA Master 2.0 combines iBasso's algorithm achievements of the last three years and is the reason why they have been able to achieve a breakthrough in discrete DAC.

1. FPGA plays the role of signal reorganisation and recoding, which generates PWM signals that can be decoded by the subsequent PWM DAC.

2 . DAC designers are aware that the presence of noise above a certain THD value is an obstacle to achieving a wider dynamic range. The iBasso D16's FPGA Master2.0 features an impressive noise shaper that radically reduces the noise floor.

3 . Global clock regeneration technology is used. Two femtosecond oscillators from Accusilicon provide a clock reference for the FPGA. The FPGA regenerates the synchronous clock with low phase noise required by the DSP and USB receiver. 1-bit DACs are very sensitive to clock jitter. iBasso tested a number of femtosecond oscillators from different brands, and Accusilicon's audio oscillator has a phase noise of only -158dBc/Hz [@1kHz]. Compared to the -145dBc/Hz of a general femtosecond oscillator, the phase noise is reduced by 13dB, which guarantees excellent jitter control for the iBasso D16.

4. precise picosecond delay control, which allows the I/O delay to be adjusted and the "wiring delay" of the card to be compensated so that the signals arriving at the DAC end are aligned and strictly synchronised.

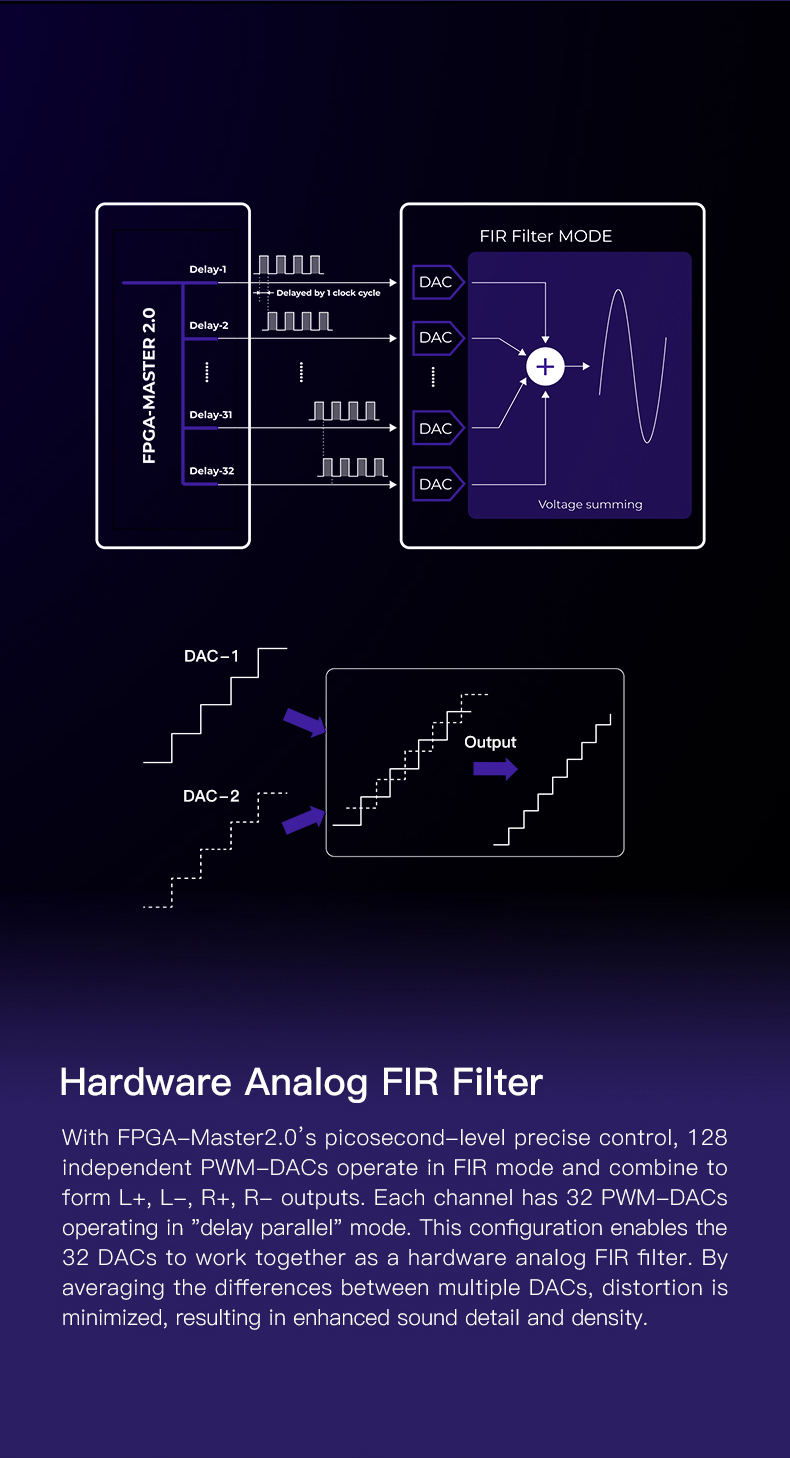

5. With the precise control of the FPGA Master 2.0, 128 independent PWM DACs operate in FIR mode and combine to form L+, L-, R+, R- outputs. Each DAC data bit is carefully delayed and aligned by rigorous compensation.

Discrete PWM DAC

After the FPGA has generated the PWM signal, it is forwarded to the discrete PWM DAC for decoding. 16 sets of an 8E PWM DAC cascade are used.

There are 4 sets per L+, L-, R+, R-, which corresponds to 32 PWM DACs. The number of DACs exceeds that of other portable discrete DACs by more than 6.4 times. With the exceptional combination of precise decoding and a significant number of extremely high quality DACs, a THD+N value of less than 0.0001% is achieved, which is an exceptional performance.

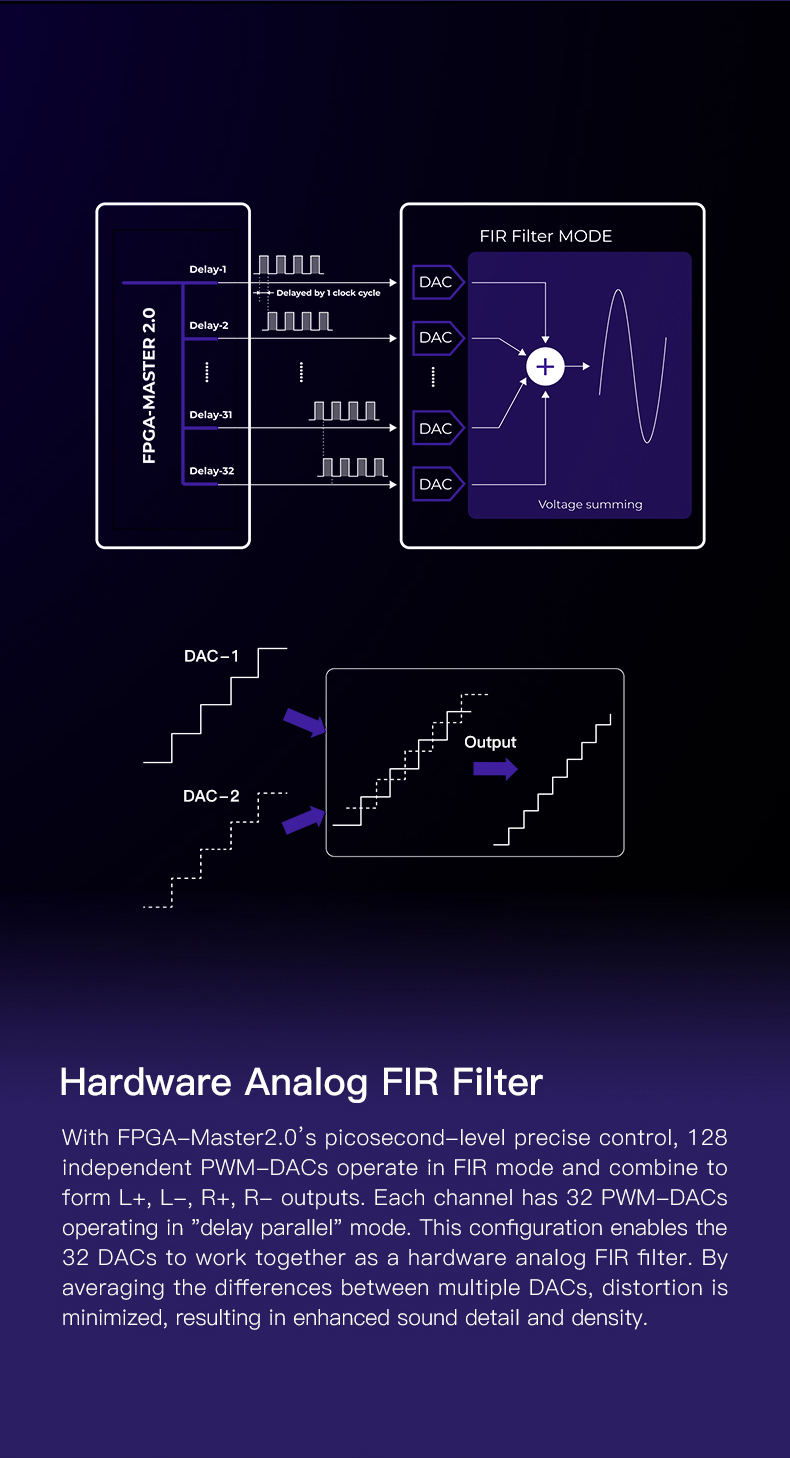

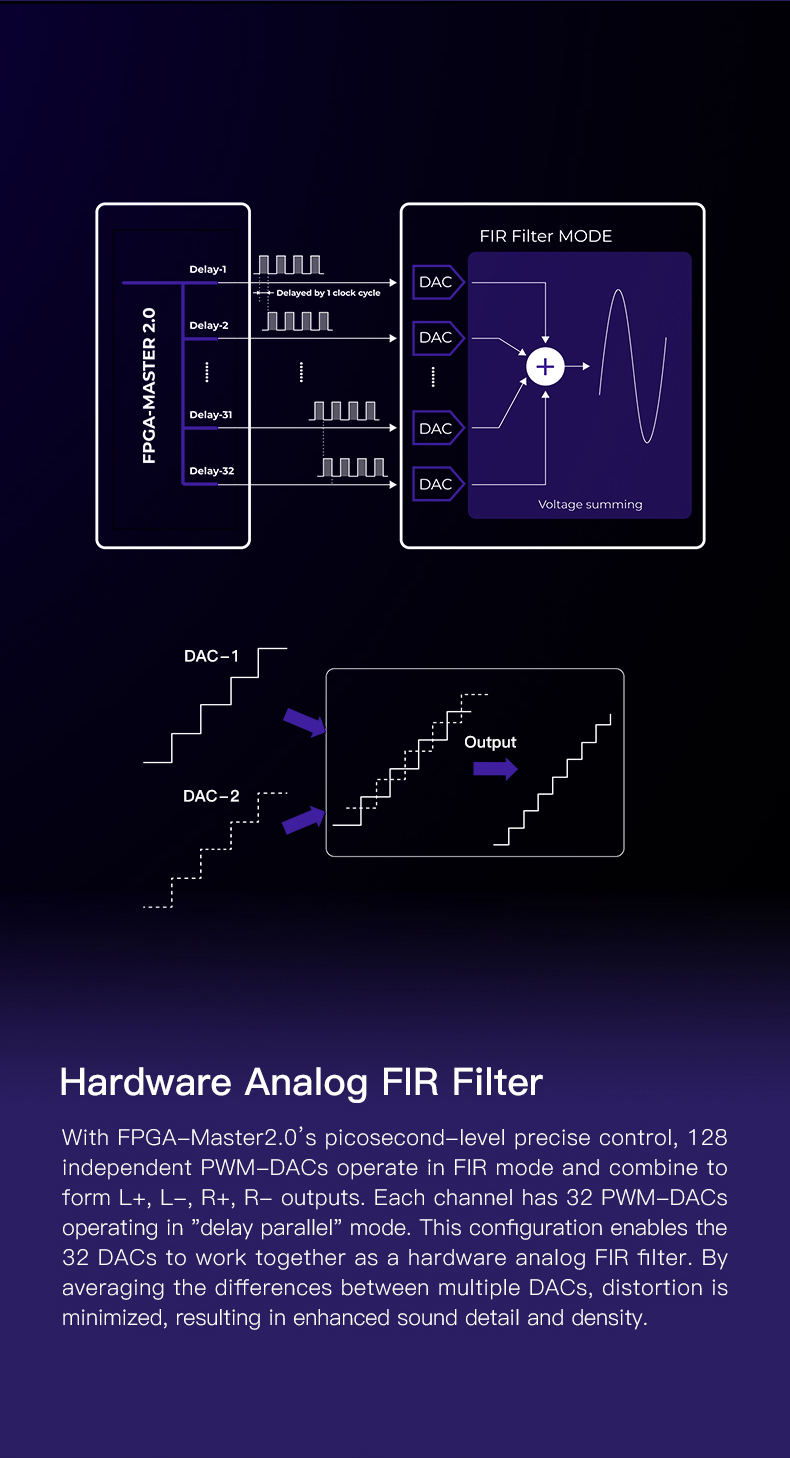

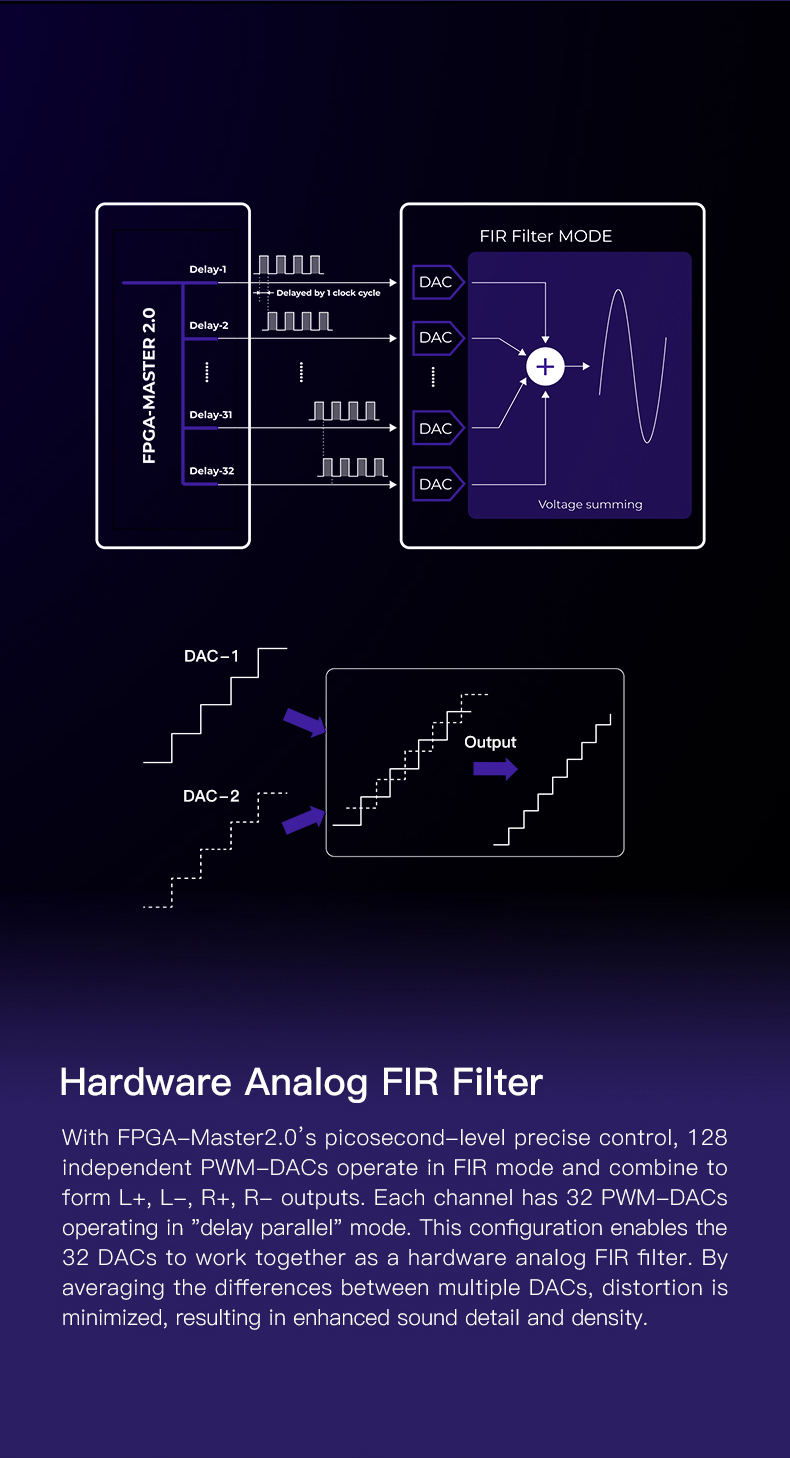

Hardware analogue FIR filter

With the FPGA-Master2.0's precise picosecond control, 128 independent PWM DACs operate in FIR mode, forming L+, L-, R+, R- outputs. Each channel has 32 PWM DACs operating in "Delay Parallel" mode.

This configuration allows the 32 DACs to work together as an analogue hardware FIR filter. By averaging the differences between multiple DACs, distortion is minimised, resulting in improved detail and sound density.

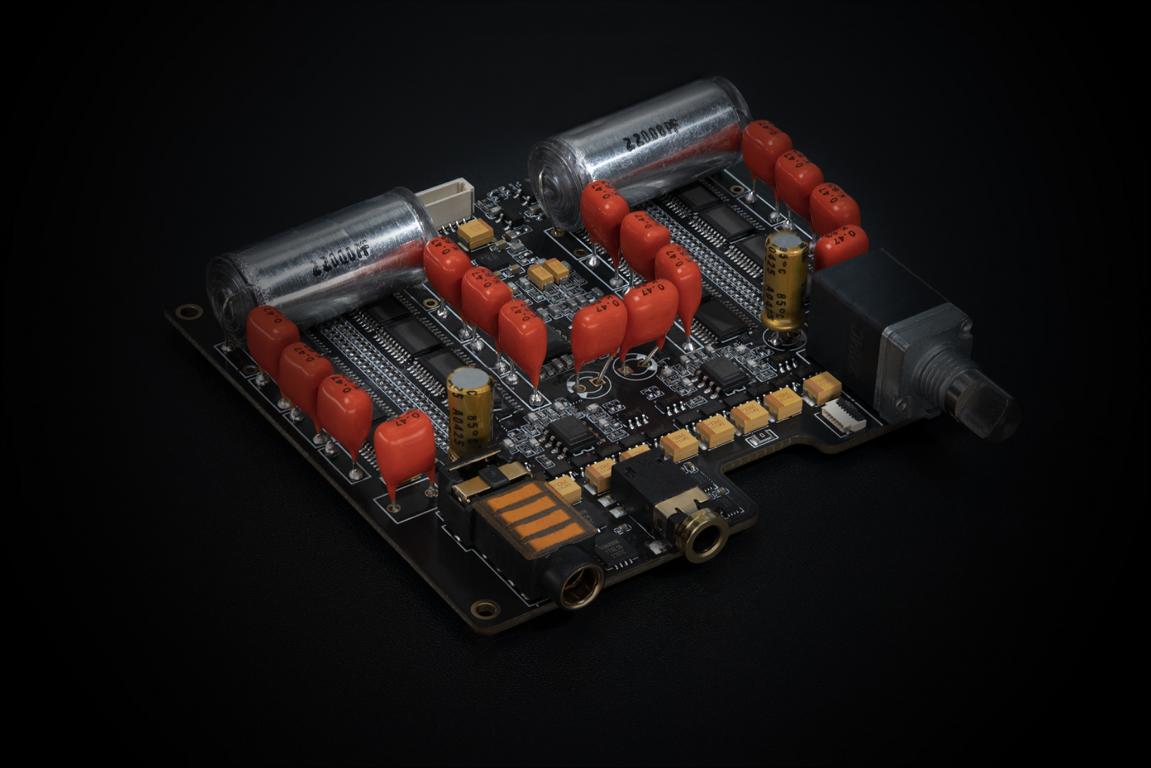

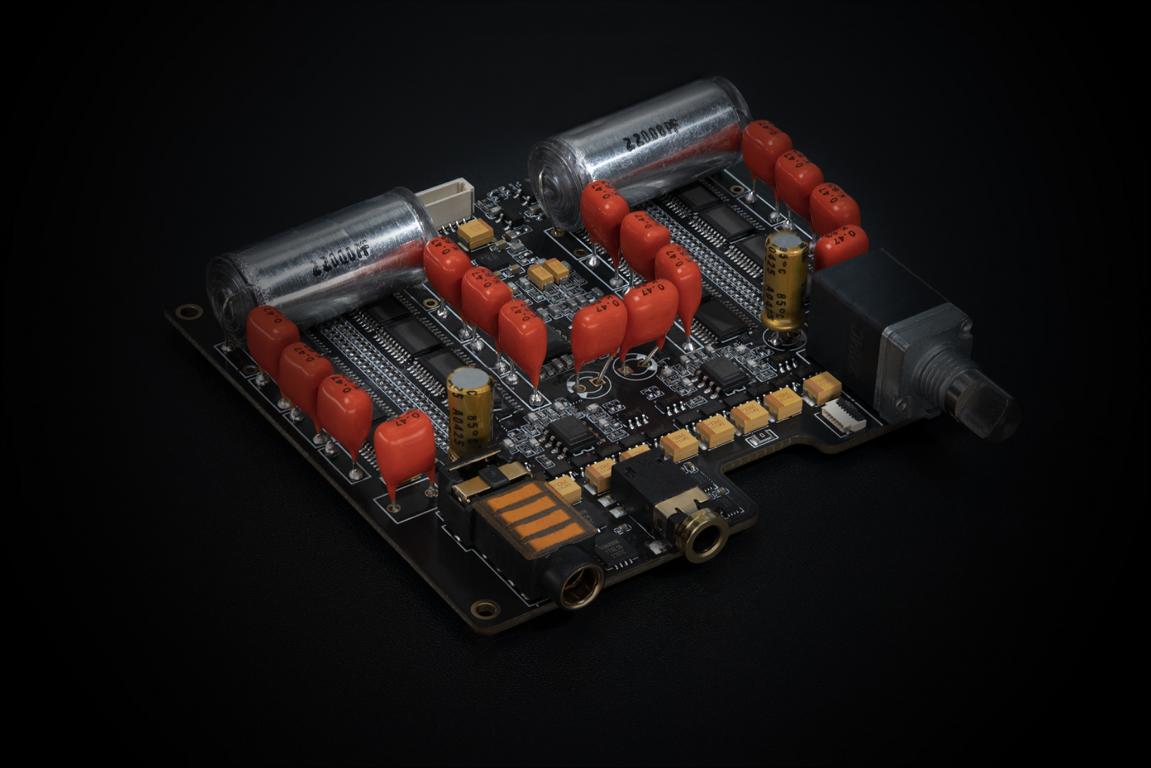

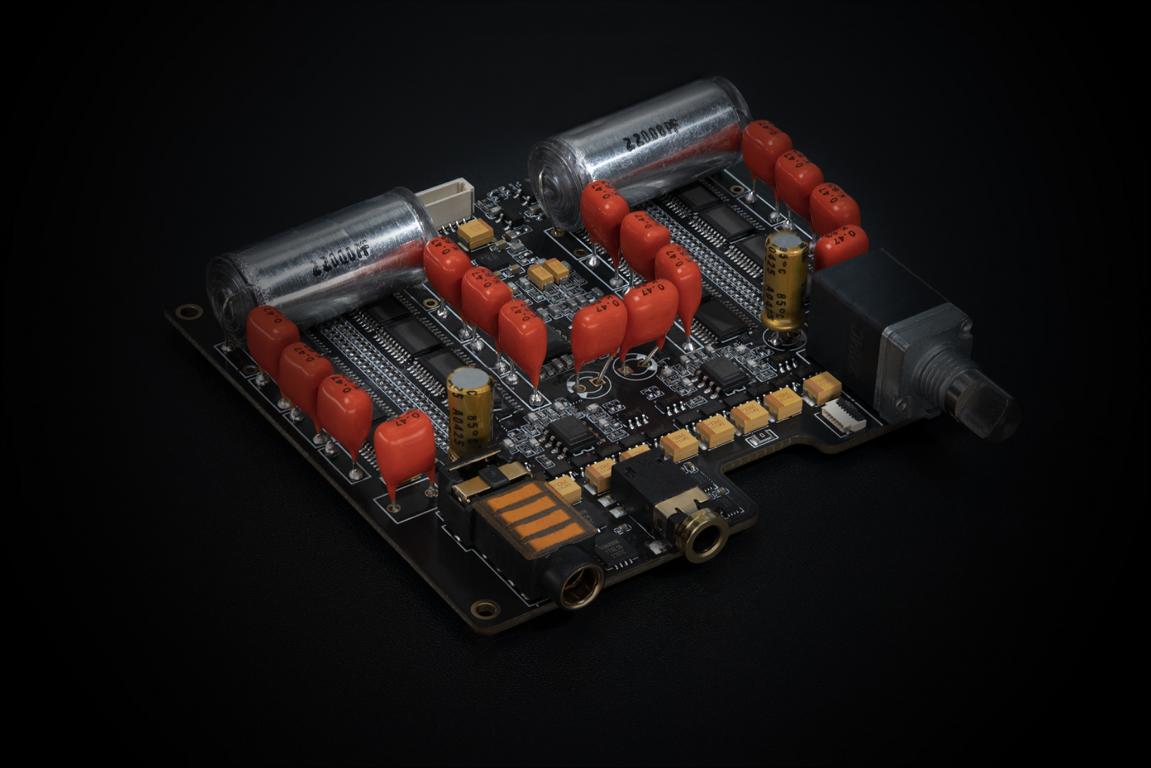

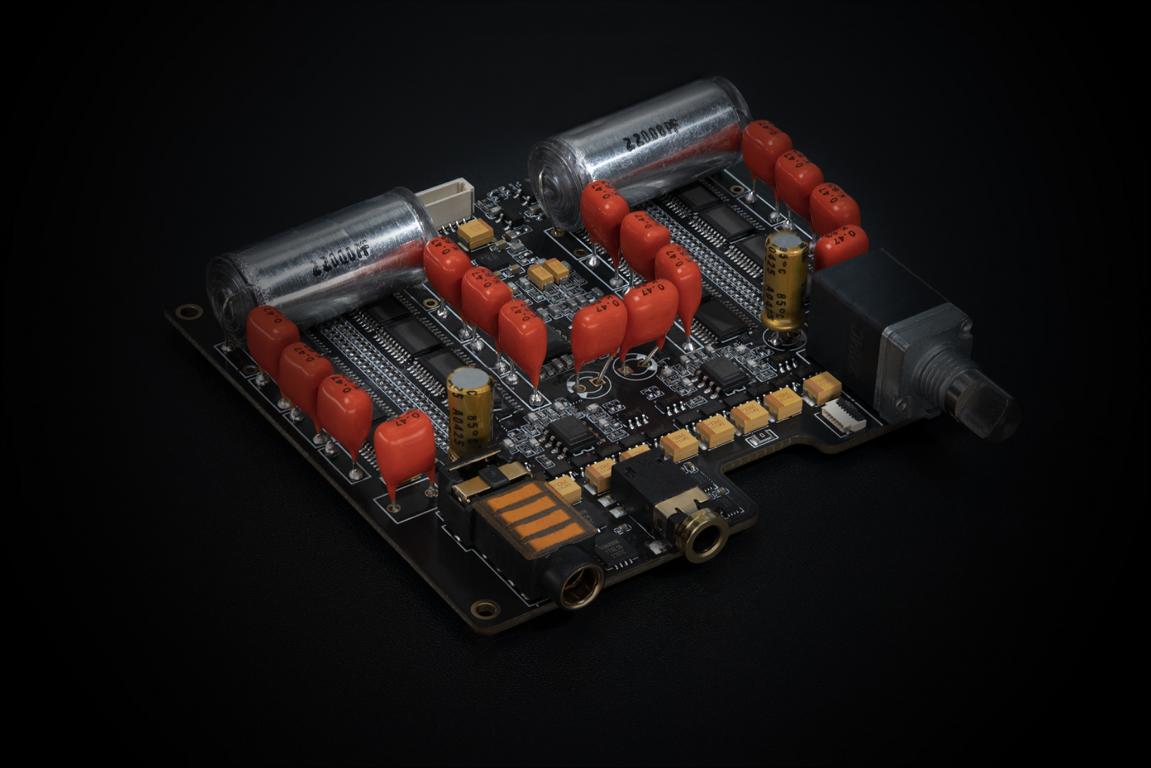

Discrete Super Class A amplifier

1125mW+1125mw@32Ω

The iBasso D16 utilises a similar architecture to the DX320 MAX, a discrete Super Class A amplifier circuit. It contains 20 pieces of Low VCEsat (BISS) dual transistors and has an impressive output current capacity of up to 2A, resulting in a robust power of 1125mW+1125mW@32Ω.

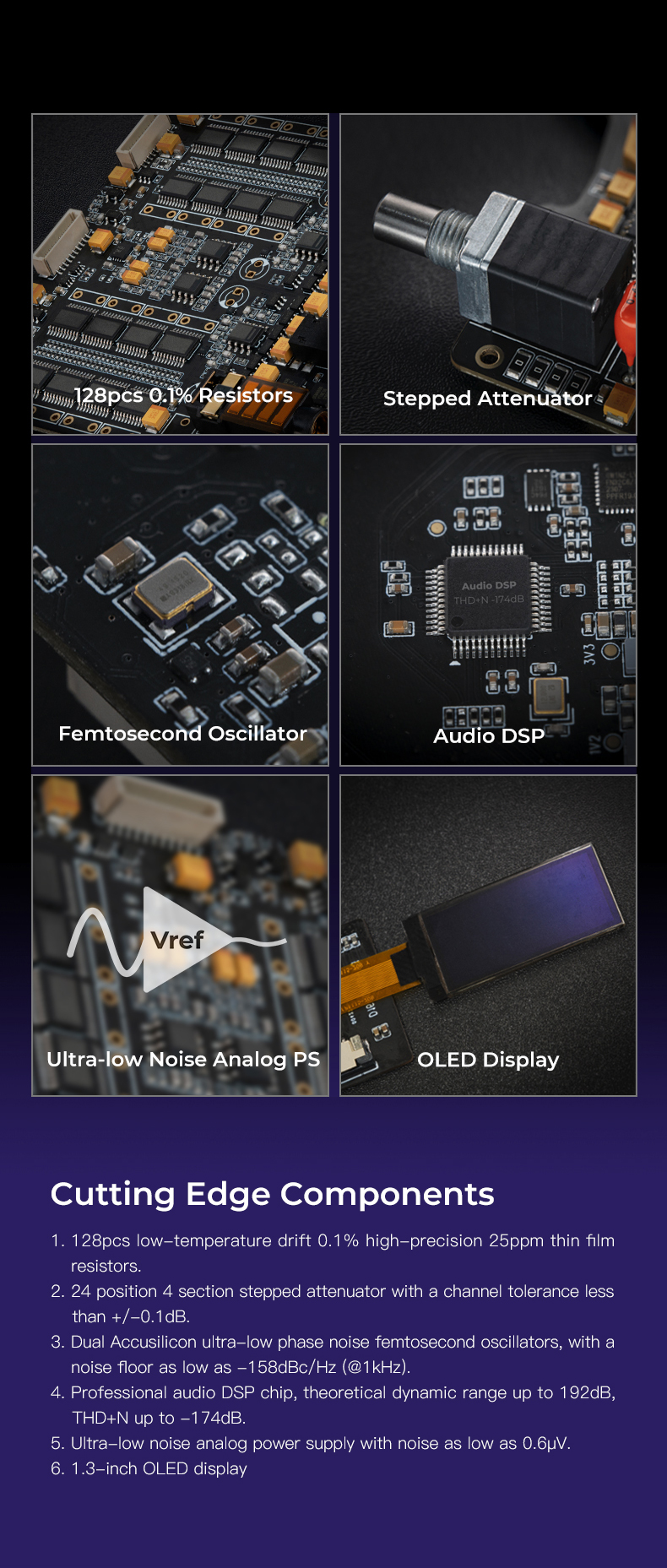

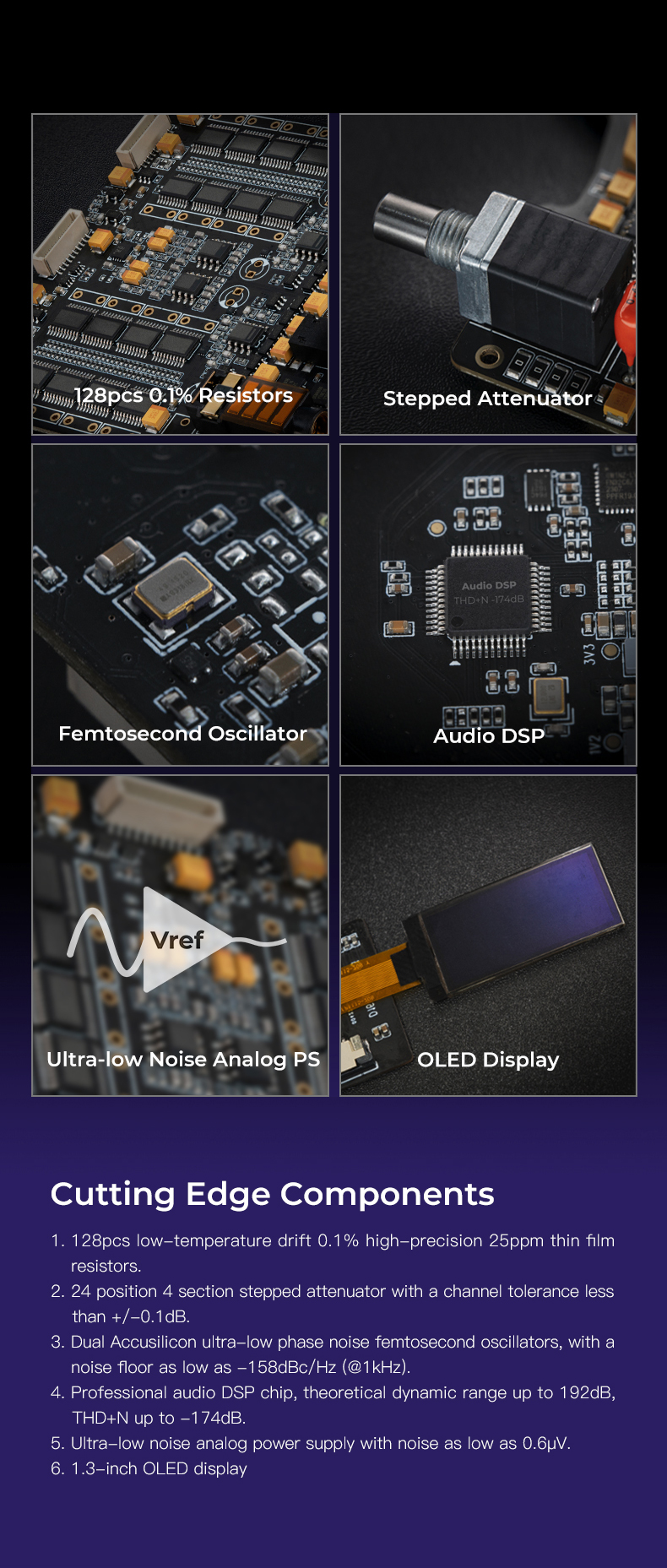

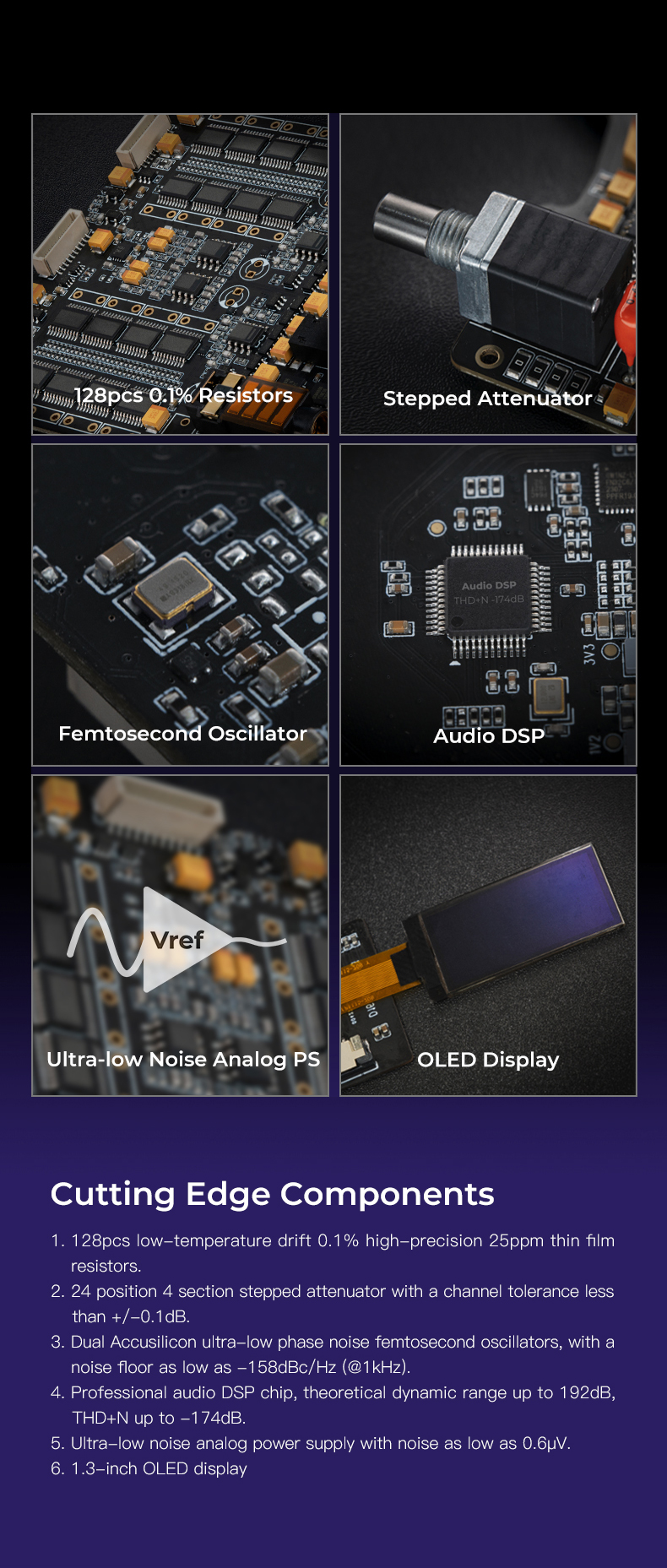

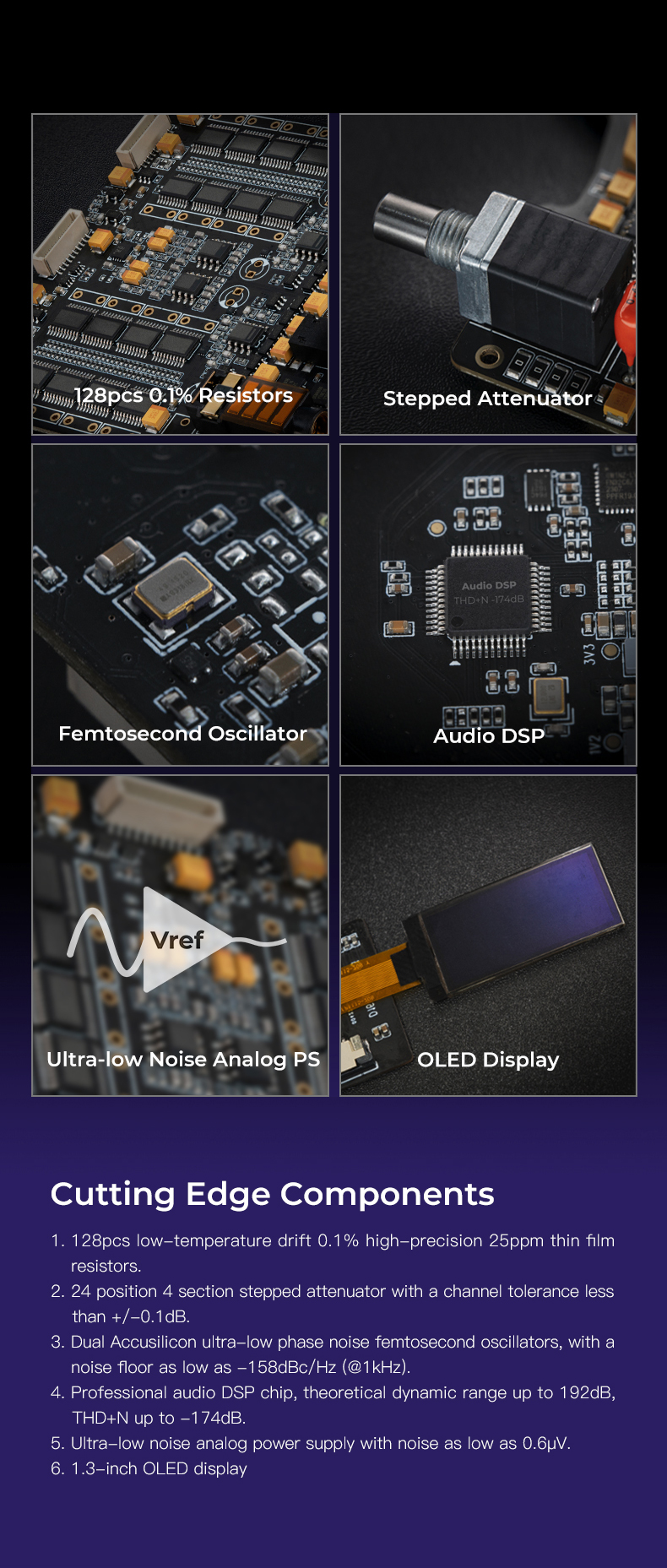

State-of-the-art components

1. 128 high-precision 25ppm thin-film resistors with 0.1% low-temperature drift.

2. 24 step attenuators with 4 sections and a channel tolerance of less than +/-0.1dB.

3. two Accusilicon femtosecond oscillators with extremely low phase noise and a noise level of only -158dBc/Hz (@1kHz).

4. professional audio DSP chip, theoretical dynamic range up to 192 dB, THD+N up to -174 dB.

5. ultra low-noise analogue power supply with a noise floor of only 0.6μV.

6. 1.3-inch OLED display

Specifications

128 pieces of 0.1% resistors

Stepped attenuator

Femtosecond oscillator

Audio DSP

Ultra low-noise

analogue PS

OLED display

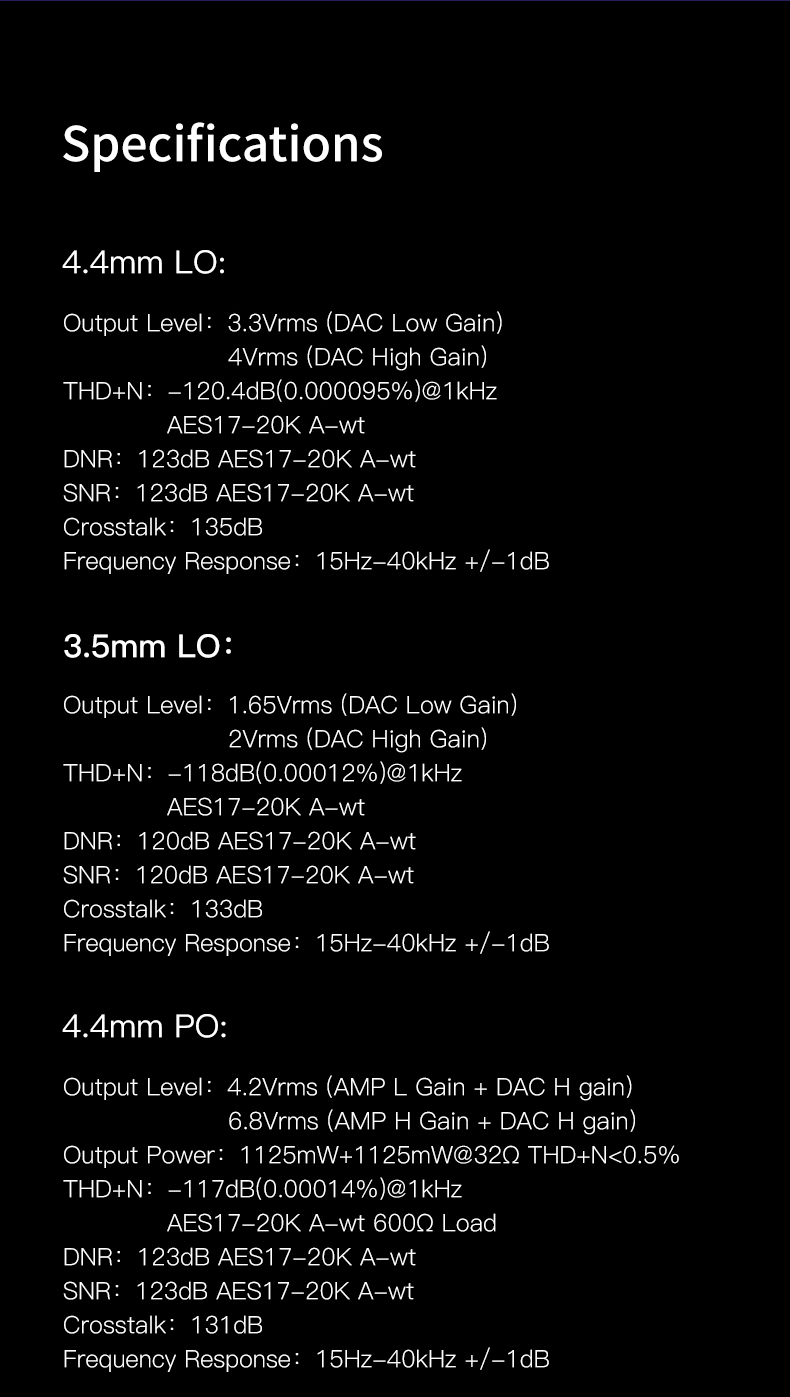

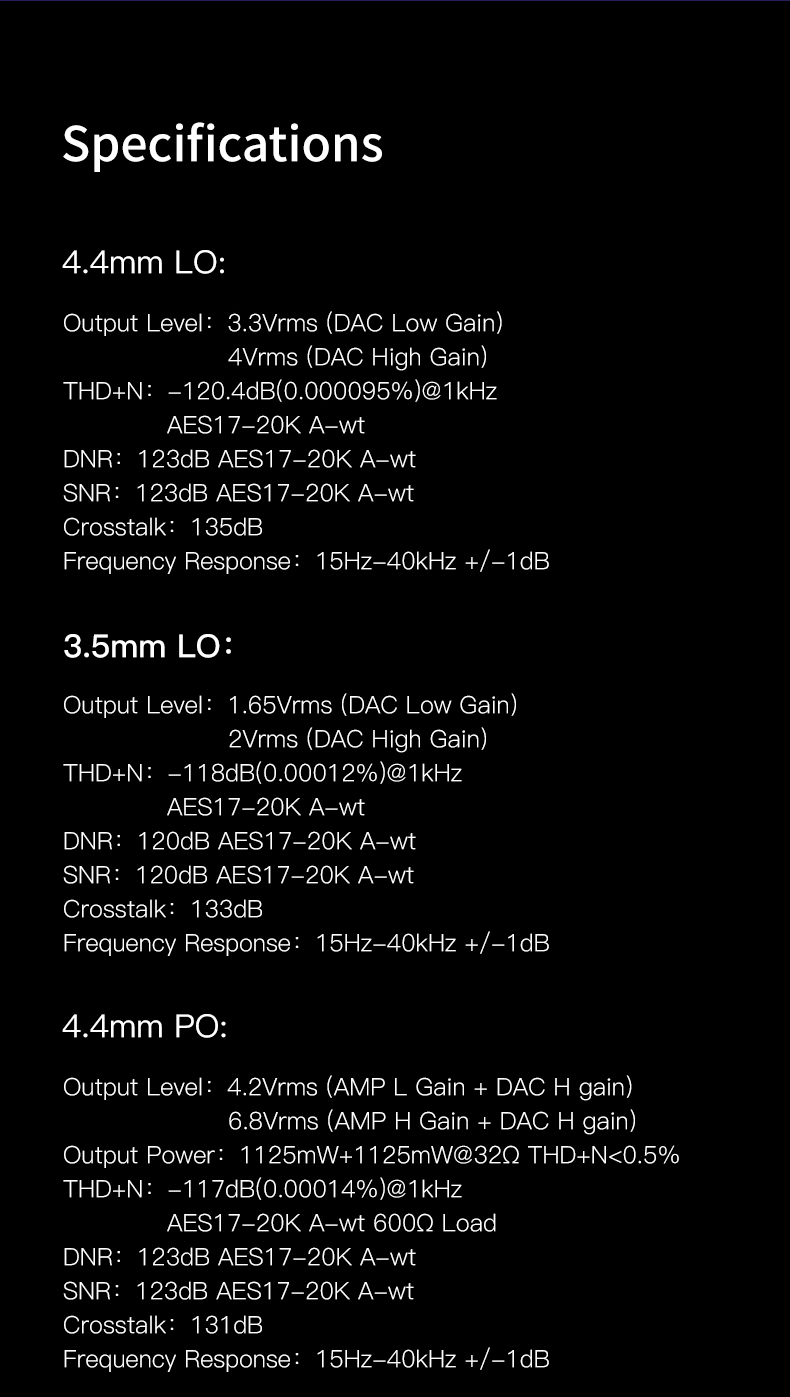

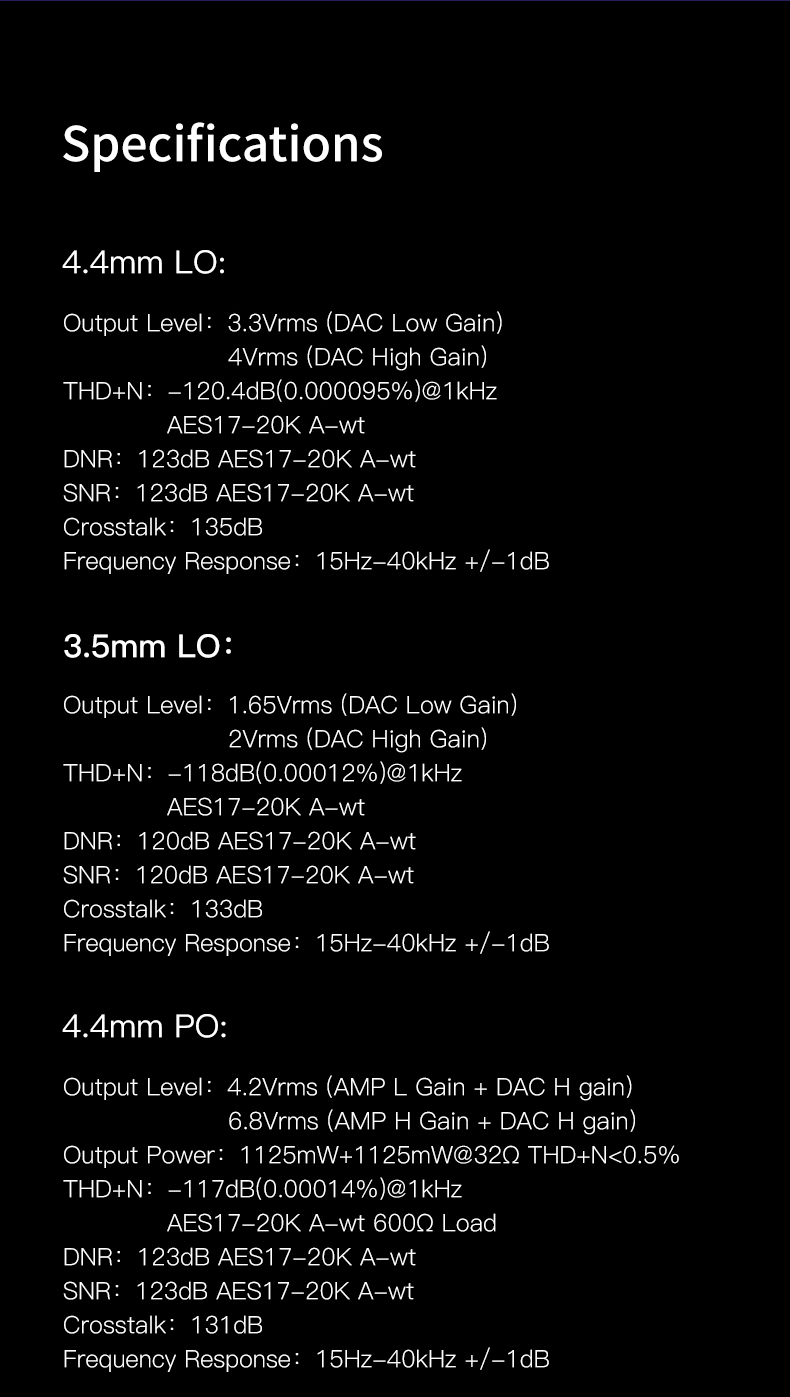

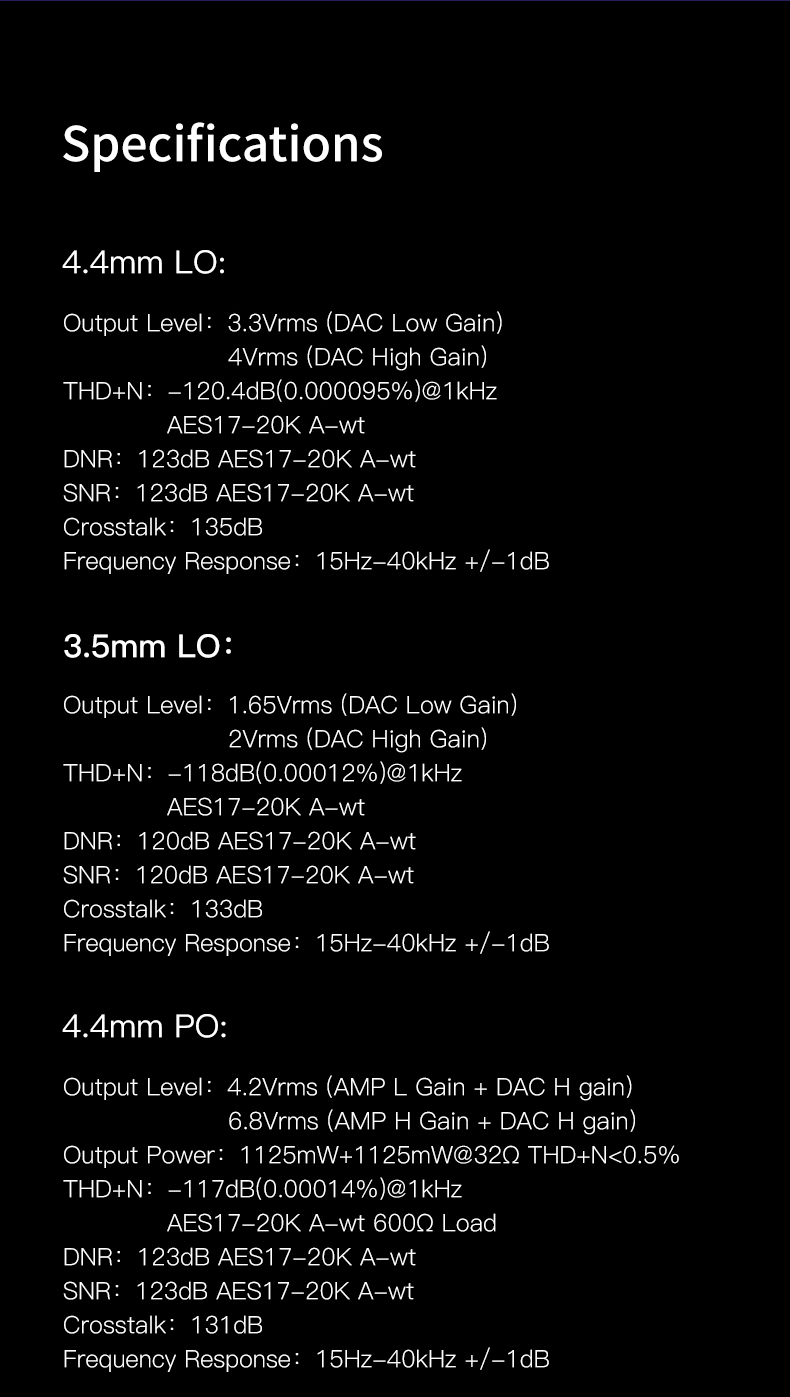

4.4mm LO

Output level:

3.3Vrms (DAC low gain)

4Vrms (DAC high gain)

THD+N:-120.4dB(0.000095%)@1kHz AES17-20K A-wt

DNR:123dB AES17-20K A-wt

SNR: 123dB AES17-20K A-wt

Crosstalk:135dB

Frequency response:15Hz-40kHz +/-1d

B 3.5mm LO

Output level:

1.65Vrms (DAC low gain)

2Vrms (DAC high gain)

THD+N:-118dB(0.00012%)@1kHz AES17-20K A-wt

DNR: 120dB AES17-20K A-wt

SNR: 120dB AES17-20K A-wt

Crosstalk:133dB

Frequency response:15Hz-40kHz +/-1dB

4.4mm PO

Output level:

4.2Vrms (AMP L gain + DAC H gain)

6.8Vrms (AMP H gain + DAC H gain)

Ausgangsleistung:1125mW +1125mW@32Ω

THD+N<0.5%

THD+N:-117dB(0.00014%)@1kHz AES17-20K A-wt 600Ω Load

DNR:123dB AES17-20K A-wt

SNR:123dB AES17-20K A-wt

Crosstalk:131dB

Frequency response:15Hz-40kHz +/-1dB

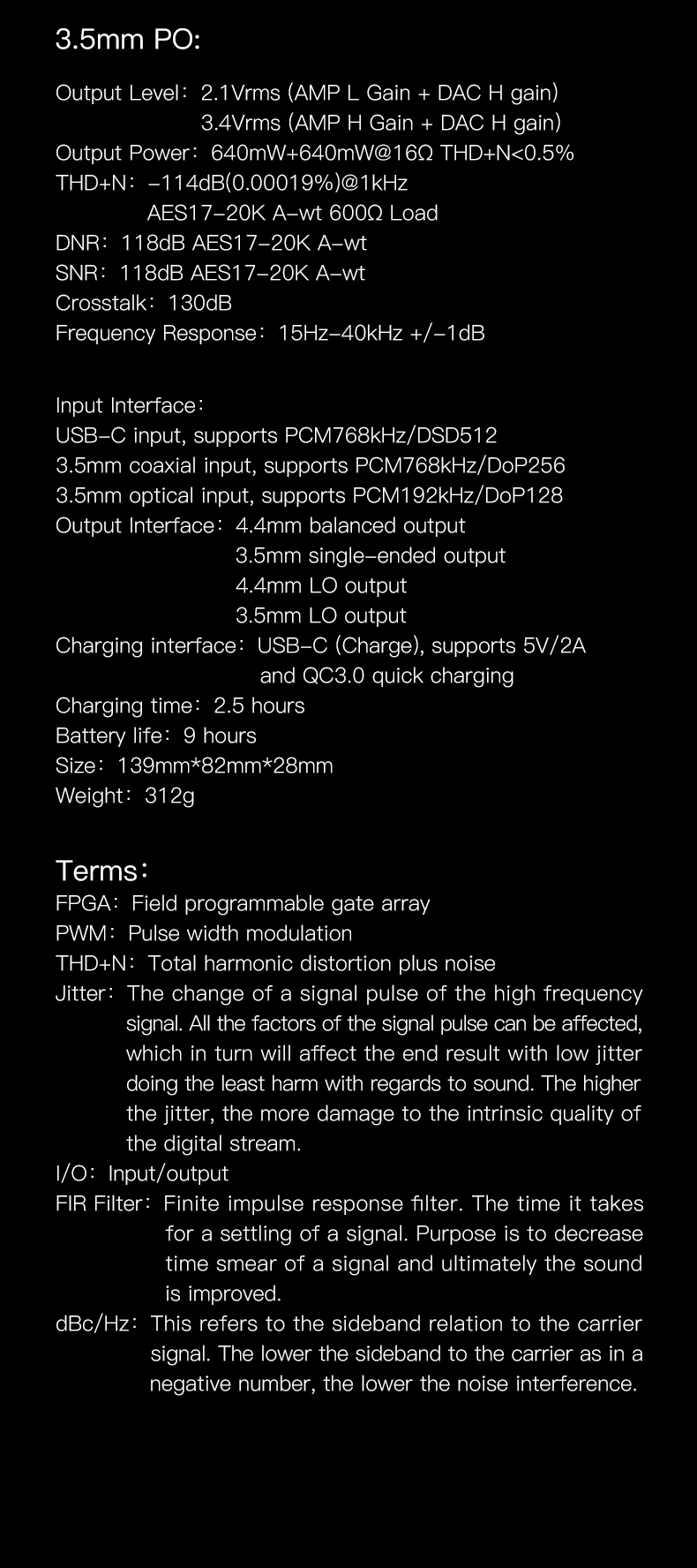

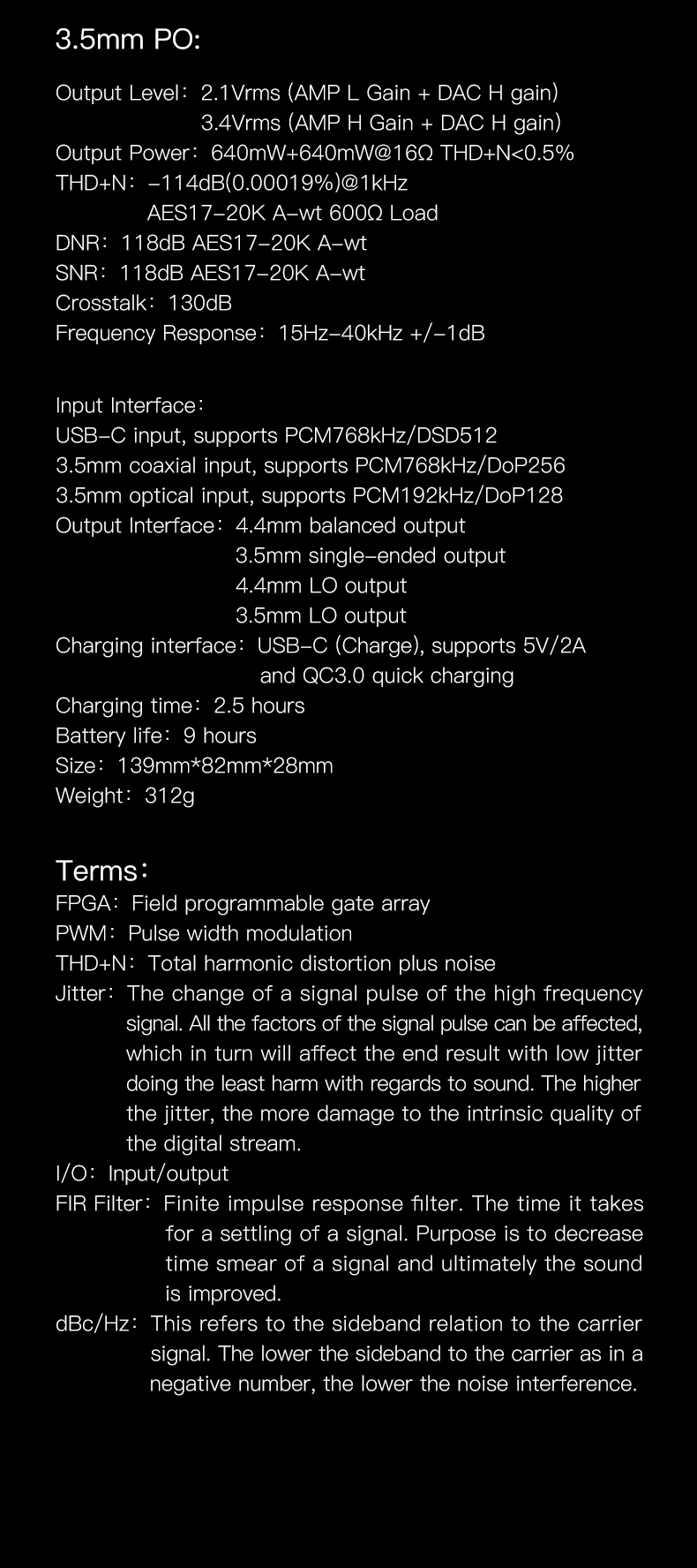

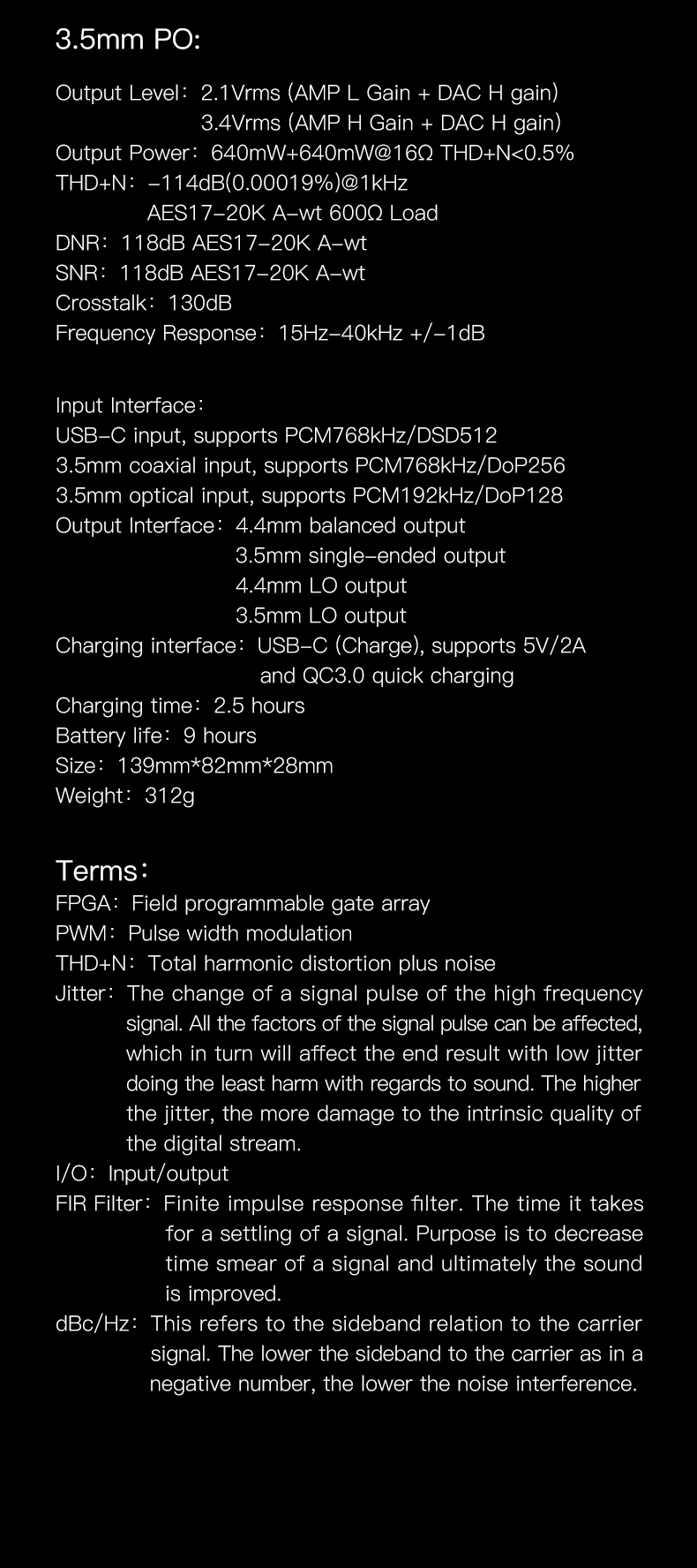

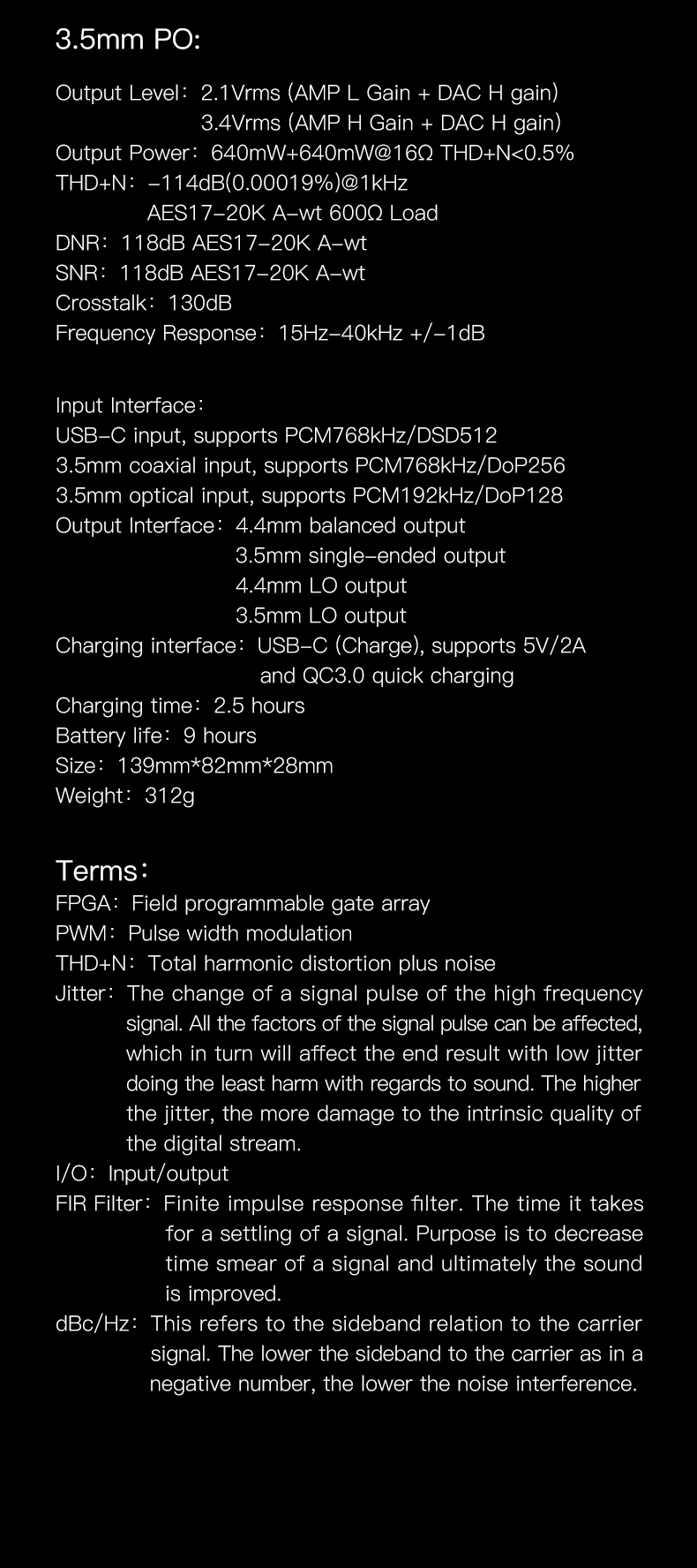

3.5mm PO

Output level:

2.1Vrms (AMP L gain + DAC H gain)

3.4Vrms (AMP H gain + DAC H gain)

Output Power:640mW+640mW@16ΩTHD+N<0.5%

THD+N:-114dB(0.00019%)@1kHz AES17-20K A-wt 600Ω Load

DNR:118dB AES17-20K A-wt

SNR:118dB AES17-20K A-wt

Crosstalk:130dB

Frequency response:15Hz-40kHz +/-1dB

Input interface

USB-C input, supports PCM768kHz/DSD512

3.5mm

coaxial input, supports PCM768kHz/DoP256

3.5 mm

optical input, supports PCM192kHz/DoP128

Output interfaces

4.4 mm balanced output

3.5 mm output (single-ended)

4.4 mm LO output

3.5 mm LO output

Charging interface: USB-C (Charge), supports 5V/2A and QC3.0 fast charging

Size: 139mm*82mm*28mm

Weight: 312g

Informationen zum Hersteller

iBasso D16 TAIPAN

- Unrivalled performance & The best portable 1-bit discrete DAC from iBasso

- FPGA Master2.0

- 16 sets of cascaded 8E PWM DACs

The iBasso D16 is a DAC that uses the iBasso-developed FPGA-Master2.0 as its core and utilises 16 sets of cascaded 8E PWM DACs with a total of 128 PWM DACs (discrete) for 1-bit D/A conversion. The measured THD+N value is over 0.0001%, which is the best value among current portable discrete DACs. The AMP section is a super class A transistor amplifier very similar to the iBasso DX320 MAX amplifier.

FPGA Master 2.0

The D16's FPGA Master 2.0 combines iBasso's algorithm achievements of the last three years and is the reason why they have been able to achieve a breakthrough in discrete DAC.

1. FPGA plays the role of signal reorganisation and recoding, which generates PWM signals that can be decoded by the subsequent PWM DAC.

2 . DAC designers are aware that the presence of noise above a certain THD value is an obstacle to achieving a wider dynamic range. The iBasso D16's FPGA Master2.0 features an impressive noise shaper that radically reduces the noise floor.

3 . Global clock regeneration technology is used. Two femtosecond oscillators from Accusilicon provide a clock reference for the FPGA. The FPGA regenerates the synchronous clock with low phase noise required by the DSP and USB receiver. 1-bit DACs are very sensitive to clock jitter. iBasso tested a number of femtosecond oscillators from different brands, and Accusilicon's audio oscillator has a phase noise of only -158dBc/Hz [@1kHz]. Compared to the -145dBc/Hz of a general femtosecond oscillator, the phase noise is reduced by 13dB, which guarantees excellent jitter control for the iBasso D16.

4. precise picosecond delay control, which allows the I/O delay to be adjusted and the "wiring delay" of the card to be compensated so that the signals arriving at the DAC end are aligned and strictly synchronised.

5. With the precise control of the FPGA Master 2.0, 128 independent PWM DACs operate in FIR mode and combine to form L+, L-, R+, R- outputs. Each DAC data bit is carefully delayed and aligned by rigorous compensation.

Discrete PWM DAC

After the FPGA has generated the PWM signal, it is forwarded to the discrete PWM DAC for decoding. 16 sets of an 8E PWM DAC cascade are used.

There are 4 sets per L+, L-, R+, R-, which corresponds to 32 PWM DACs. The number of DACs exceeds that of other portable discrete DACs by more than 6.4 times. With the exceptional combination of precise decoding and a significant number of extremely high quality DACs, a THD+N value of less than 0.0001% is achieved, which is an exceptional performance.

Hardware analogue FIR filter

With the FPGA-Master2.0's precise picosecond control, 128 independent PWM DACs operate in FIR mode, forming L+, L-, R+, R- outputs. Each channel has 32 PWM DACs operating in "Delay Parallel" mode.

This configuration allows the 32 DACs to work together as an analogue hardware FIR filter. By averaging the differences between multiple DACs, distortion is minimised, resulting in improved detail and sound density.

Discrete Super Class A amplifier

1125mW+1125mw@32Ω

The iBasso D16 utilises a similar architecture to the DX320 MAX, a discrete Super Class A amplifier circuit. It contains 20 pieces of Low VCEsat (BISS) dual transistors and has an impressive output current capacity of up to 2A, resulting in a robust power of 1125mW+1125mW@32Ω.

State-of-the-art components

1. 128 high-precision 25ppm thin-film resistors with 0.1% low-temperature drift.

2. 24 step attenuators with 4 sections and a channel tolerance of less than +/-0.1dB.

3. two Accusilicon femtosecond oscillators with extremely low phase noise and a noise level of only -158dBc/Hz (@1kHz).

4. professional audio DSP chip, theoretical dynamic range up to 192 dB, THD+N up to -174 dB.

5. ultra low-noise analogue power supply with a noise floor of only 0.6μV.

6. 1.3-inch OLED display

Specifications

128 pieces of 0.1% resistors

Stepped attenuator

Femtosecond oscillator

Audio DSP

Ultra low-noise

analogue PS

OLED display

4.4mm LO

Output level:

3.3Vrms (DAC low gain)

4Vrms (DAC high gain)

THD+N:-120.4dB(0.000095%)@1kHz AES17-20K A-wt

DNR:123dB AES17-20K A-wt

SNR: 123dB AES17-20K A-wt

Crosstalk:135dB

Frequency response:15Hz-40kHz +/-1d

B 3.5mm LO

Output level:

1.65Vrms (DAC low gain)

2Vrms (DAC high gain)

THD+N:-118dB(0.00012%)@1kHz AES17-20K A-wt

DNR: 120dB AES17-20K A-wt

SNR: 120dB AES17-20K A-wt

Crosstalk:133dB

Frequency response:15Hz-40kHz +/-1dB

4.4mm PO

Output level:

4.2Vrms (AMP L gain + DAC H gain)

6.8Vrms (AMP H gain + DAC H gain)

Ausgangsleistung:1125mW +1125mW@32Ω

THD+N<0.5%

THD+N:-117dB(0.00014%)@1kHz AES17-20K A-wt 600Ω Load

DNR:123dB AES17-20K A-wt

SNR:123dB AES17-20K A-wt

Crosstalk:131dB

Frequency response:15Hz-40kHz +/-1dB

3.5mm PO

Output level:

2.1Vrms (AMP L gain + DAC H gain)

3.4Vrms (AMP H gain + DAC H gain)

Output Power:640mW+640mW@16ΩTHD+N<0.5%

THD+N:-114dB(0.00019%)@1kHz AES17-20K A-wt 600Ω Load

DNR:118dB AES17-20K A-wt

SNR:118dB AES17-20K A-wt

Crosstalk:130dB

Frequency response:15Hz-40kHz +/-1dB

Input interface

USB-C input, supports PCM768kHz/DSD512

3.5mm

coaxial input, supports PCM768kHz/DoP256

3.5 mm

optical input, supports PCM192kHz/DoP128

Output interfaces

4.4 mm balanced output

3.5 mm output (single-ended)

4.4 mm LO output

3.5 mm LO output

Charging interface: USB-C (Charge), supports 5V/2A and QC3.0 fast charging

Size: 139mm*82mm*28mm

Weight: 312g

EU-Verantwortlicher

NT Global Distribution GmbH

Buntentorsdeich 10

28201 Bremen

Deutschland

www.nt-global.de

info@nt-global.com

iBasso DX320 Max Ti

€3,499.00*

iBasso DX320 MAX Ti - The new flagship from iBasso- Limited to 888 pieces worldwide -Available soon / Due to high demand, we have only been able to order a small number of the DX320 MAX Ti from iBasso for Europe. Due to very tight availability, we are allowing pre-orders on this item.

5.0-inch IPS display (1080*1920), with capacitive on-cell touch panel.

Four BD34301EKV ROHM DAC chips are integrated.

6GB LPDDR4X + 128GB ROM.

Android 11 + Mango OS.

The digital and analogue parts of the DX320MAX are powered separately, with each part having an independent charging system. The digital and analogue hardware and signal communication use optocouplers and I2C isolators to completely isolate the digital and analogue sections from any interference.The AMP section is powered by a true +/- 8.4 V battery pack. No voltage boost is used, ensuring the highest purity and current output.An optimised super class A discrete amplifier circuit is built in. It eliminates the switching distortion of transistors while providing the sound signature of a class A amplifier. Furthermore, it significantly reduces heat generation.The DX320MAX has versatile outputs that include a balanced 4.4 mm jack output and a 3.5 mm jack output.The output voltage of the 3.5 mm jack output is up to 4.5 V RMS, while that of the balanced jack output is up to 9 V RMS.Electrolytic capacitors and film capacitors are used in the DX320MAX.A matched analogue 4-wiper stage attenuator with a channel tolerance of less than +/-0.1 dB has been selected.Specifications4 settings for physical gain control.Bit by bit playback with support up to 32bit/768kHz.Support for native DSD up to and including 512x.14nm Octa-Core Qualcomm Snapdragon 660 SoC.FPGA master, a dedicated controller for the audio system.2 Accusilicon femtosecond oscillators with ultra-low phase noise.QC3.0 and PD3.0 fast charging support for the digital part.USB digital output that outputs up to PCM 32bit/384kHz, Native DSD256 and DoP DSD128.Mini coaxial output supporting up to 24bit/384kHz and DoP DSD128.Support for 2.4G & 5G WiFi, Bluetooth 5.0.Support for SDXC and SDHC micro SD cards up to and including 2TB.Supports USB3.1 super speed transmission.USB DAC function supporting up to 32bit/384kHz and DoP DSD128.Supported audio formats: MQA, APE, FLAC, WAV, WMA, AAC, ALAC, AIFF, OGG, MP3, DFF, DSF, and DXD.